[문서] eASIC (Customer Story) 관리자 | 2021.09.27 | 조회 1227 첨부파일 :

Quick, Customizable Semiconductor Device Designs

eASIC은 Single Mask Adaptable ASIC ™ (application-specific integrated circuits) 전문 fabless 반도체 회사입니다. 고객의 특정 요구 사항을 염두에 두고 설계된 광범위한 Application에 대한 맞춤형 Integrated Circuits을 생산합니다. 특히 신제품 개발 단계에서 고객을 효과적으로 지원하려면 빠르고 비용 효율적인 설계 및 제조 프로세스가 필요합니다.고속 Application 전용 Chip 설계 시, 중요한 것은 IC 자체의 동작 만이 아닙니다. Package 및 인쇄 회로 기판 (PCB)을 포함한 전체 채널이 성능에 영향을 미칩니다. eASIC는 설계 단계에서 PCB Layout을 고려함으로써 장치의 성능을 개선하고 설치 후 발생하는 문제의 위험을 줄일 수 있습니다.

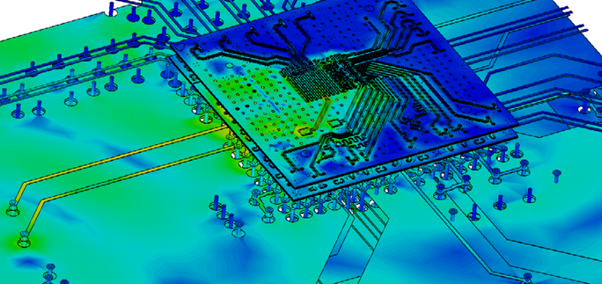

Simulating the Complex Package-PCB Interface

전자기 시뮬레이션을 통해 엔지니어는 제조에 착수하기 전, 설계의 특성을 확인할 수 있습니다. PCB는 크고 복잡하지만 Package는 작고 복잡하기 때문에 한 번에 전체 시스템을 모델링하는 것은 계산 집약적이며 긴 시뮬레이션 시간과 많은 메모리 소비가 필요합니다. 이러한 이유로 eASIC은 시뮬레이션을 분할해 Package와 PCB를 별도로 모델링하기로 했습니다.이를 위해 eASIC은 Full-wave 3D 시뮬레이션 Tool인 CST Studio Suite를 선택했습니다. CST Studio Suite에는 시뮬레이션을 연계하고 cascade 할 수 있는 SAM (System Assembly and Modeling)이 포함 되어있어 시스템을 부품의 합으로 간주할 수 있습니다. 기존의 결합된 Package / PCB 모델은 두 부품을 분리하기 위해 나누었고 Interface에 reference plane이 있는 포트를 사용하여 연결되었습니다.

CST Studio Suite의 세분화 접근 방식을 통한 Package-PCB 공동 설계는 합리적인 시간에 비용 효율적인 서버 시스템에 장착된 모델과의 상호 연결에 대한 정확한 분석에서 3D EM 시뮬레이션 강도를 활용할 수 있도록 했습니다. 이것은 복잡한 디자인에서 Full 3D 시뮬레이션을 현실로 만드는 놀라운 방법입니다!”

- LianKheng Teoh / Manager for Package Design, eASIC -

Accurate Full-Wave Simulations in Half the Time

전체 모델의 시뮬레이션에 비해 SAM을 사용한 co-simulation은 훨씬 더 빠르고 계산 부담도 적었습니다. Co-simulation 결과는 Full-simulation 결과 및 실제 측정과 거의 일치했습니다. 또한 Time-Domain Reflectometry(TDR)과 같이 널리 사용되는 실험실 측정을 정확하게 모사할 수 있었습니다.CST Studio Suite를 사용하고 모델을 분할함으로써 eASIC은 전체 모델을 사용하는 시뮬레이션과 비교할 때 Multi-level PCB 및 Package 시뮬레이션에서 최대 5배의 속도 향상을 달성할 수 있었습니다. 이는 eASIC에 상당한 속도 이점을 제공하고 설계 프로세스를 단축하는데 도움이 되었습니다.

■ 원문은 다쏘시스템즈 홈페이지에서 확인 가능합니다.

https://www.3ds.com/insights/customer-stories/easic