[문서] PCB와 Ground 간 커플링의 EMC Simulation(Using CST) 관리자 | 2024.03.14 | 조회 151 첨부파일 : PCB와 접지면 간 커플링의 EMC 시뮬레이션.pdf

본 자료에서는 CST Studio Suite®를 사용한 Simulation이 제품의 emission 성능을 개선하는 데 어떻게 도움이 되는지 설명합니다. 인쇄 회로 기판(PCB)의 신호 트레이스와 Ground 사이의 결합은 일반적으로 전자파 적합성(EMC)적 특성으로 이러한 관점이 분석이 필요합니다. 아래 소개된 내용은 Conducted emission에 대해 논의하지만 Radiated emission로 확장할 수 있습니다.

Conducted emission 테스트 배경

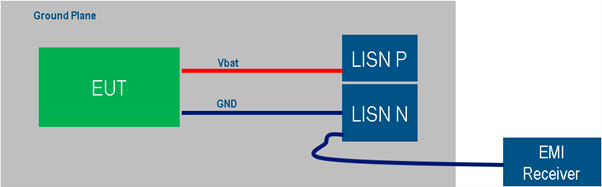

Conducted emission(CE) 테스트는 전선의 전류 또는 라인 임피던스 안정화 네트워크(LISN) 측정 포트의 전압을 측정하는 것으로 구성됩니다. 자동차 분야에서 테스트 설정은 테스트 대상 장비(EUT), 전선, LISN, EMI(전자파 간섭) 수신기, CAN과 같은 통신 장치, 부하(필요한 경우) 및 자동차 섀시를 나타내며 전압 기준을 나타내는 Ground으로 구성됩니다.

그림 1은 간단한 테스트 설정을 설명합니다: Vbat 및 GND는 각각 전원 공급 장치의 양극 및 음극용 전선을 나타냅니다. 이 경우의 EUT는 단순한 "인쇄 회로 기판(PCB)"이지만 다른 전기 또는 전자 시스템을 나타낼 수도 있습니다. CE 테스트 중 EMC 성능은 측정된 전압/전류를 자동차 분야에서 가장 많이 적용되는 표준인 CISPR 25와 같은 표준에서 정의한 한계와 비교하는 것으로 구성됩니다. 저희의 경우 전압 방식에 중점을 둡니다. 전압 방식과 전류 방식에 의한 테스트는 동등하기 때문에 측정 방법의 선택은 제한이 없습니다.

EUT 설명

이 테스트에서 EUT는 신호에 의해 여기된 하나의 트레이스와 여러 개의 접지층으로 구성된 간단한 PCB입니다. 이를 사용하여 트레이스와 Ground 사이의 결합과 레이아웃이 이 결합에 미치는 영향을 설명합니다. 세 가지 Case를 테스트합니다

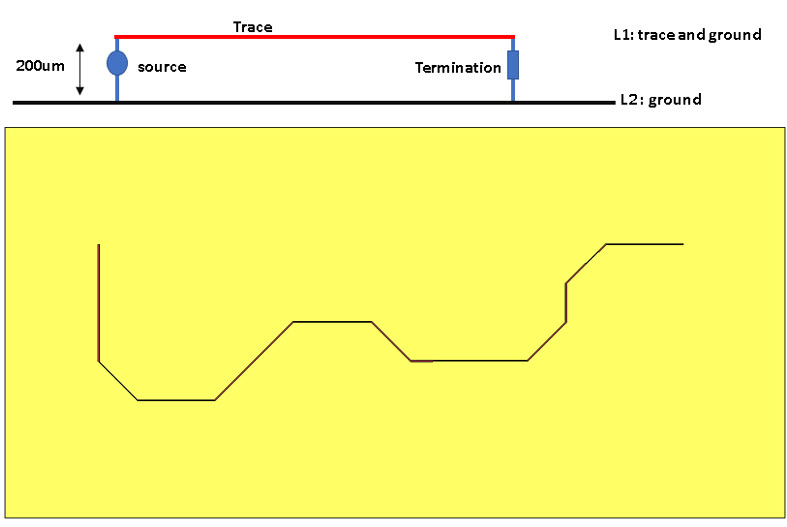

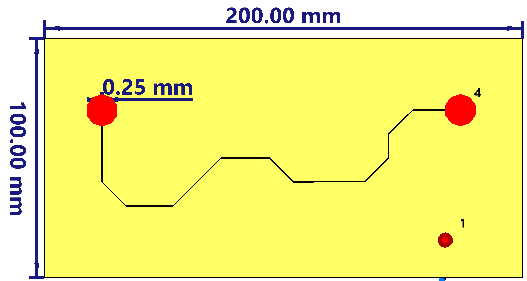

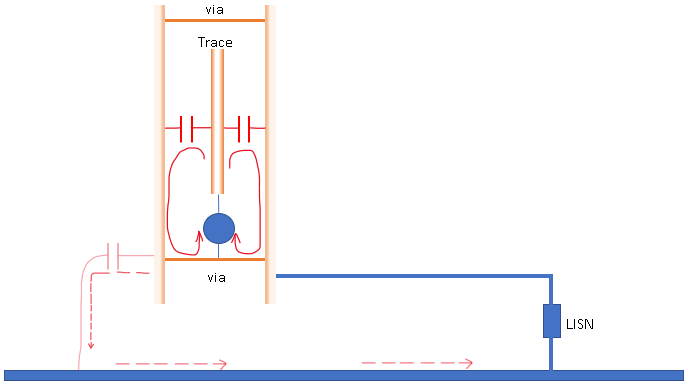

Case 1은 2레이어 PCB로 구성됩니다. GND와 트레이스로 구성됩니다. (그림 2 참조).

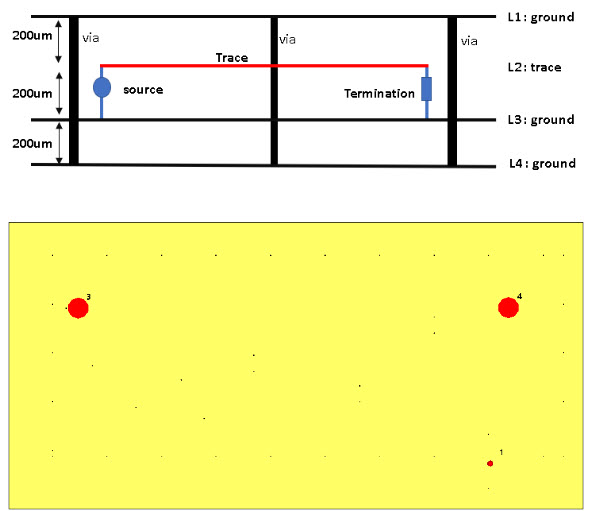

Case 2는 전파 신호를 위한 두 개의 솔리드 PCB 레퍼런스 레이어 사이에 여기 트레이스가 있는 4레이어 PCB로 구성됩니다(그림 3 참조).

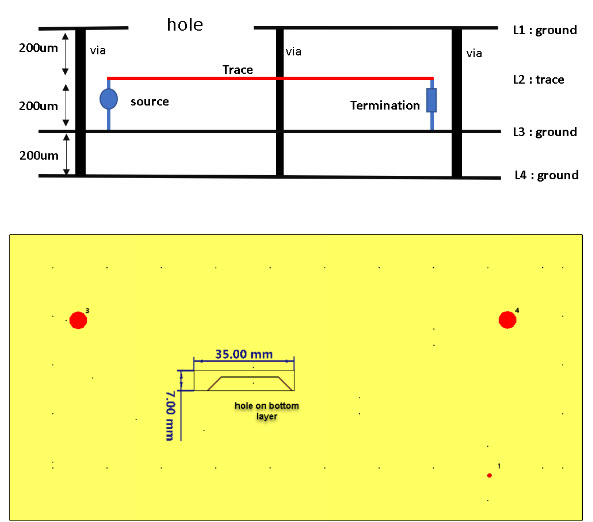

Case 3은 Case 2와 동일하며, 트레이스 바로 아래에 하단 레이어에 구멍이 있습니다(그림 4 참조).

실제 해석 진행 시 Case 2와 Case 3은 4개가 아닌 3개 레이어로 단순화되었습니다. 실제로 L4는 모델을 단순화하고 결과 해석을 더 쉽게 하기 위해 억제되었습니다. L3과 L4 사이에는 노이즈 소스가 없고 이들 사이에 존재할 수 있는 전압은 무시할 수 있기 때문에 이러한 단순화는 최종 결과에 영향을 미치지 않습니다. 접지 레이어는 디커플링 커패시터를 통해 연결된 전력 레이어일 수도 있습니다. 이 경우 커패시터는 완벽한 것으로 간주되며 레이어 간 최소 임피던스를 갖기 위해 여러 비아를 사용하여 서로 연결됩니다. 따라서 3개의 레이어를 가진 PCB 모델은 전체 4레이어 시스템을 대표합니다.

PCB는 그림 5에서 볼 수 있듯이 직사각형 형태와 21cm x 10cm의 치수를 가지며, 트레이스 길이는 21cm, 폭은 0.25mm입니다.

Conducted emission 테스트 배경

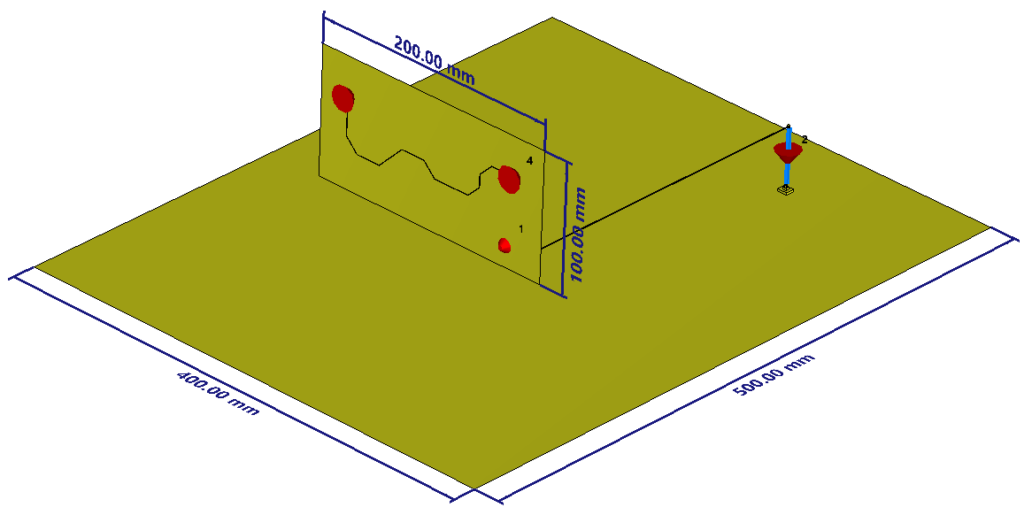

설정은 PCB와 20cm 길이의 와이어를 통해 PCB 레퍼런스를 LISN 임피던스에 연결하는 것으로 구성됩니다. 일반적으로 전원 공급 장치는 음극용 전선과 양극용 전선 두 개를 사용하여 PCB에 연결됩니다. 이 테스트에서는 이러한 전원 공급 장치 와이어를 접지 와이어 하나로만 대체합니다.

이 테스트에서는 커플링의 가장 지배적인 모드인 공통 모드만 고려합니다. 실제로 음극선과 양극선 사이의 입력 임피던스는 무시할 수 있는 수준입니다. 일반적으로 커패시터로 연결되며, 이 테스트에서는 커패시터 연결이 이상적이라고 가정합니다.

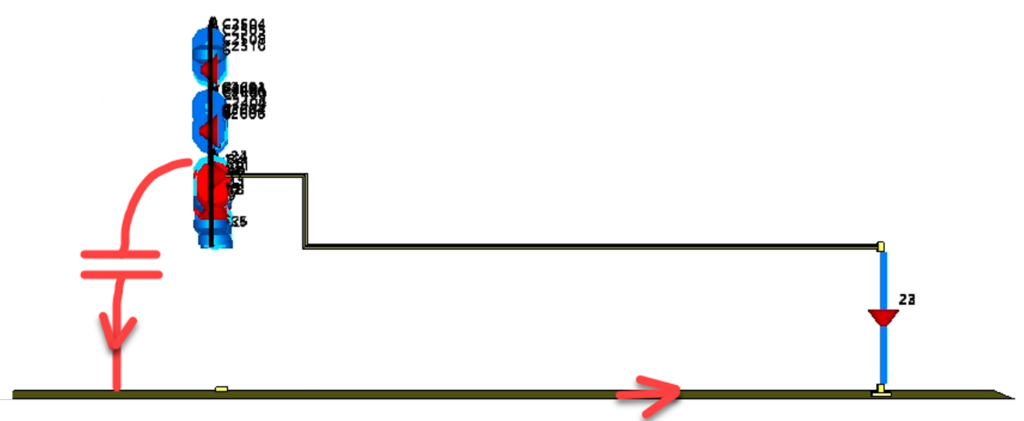

테스트 설정의 3D 모델은 그림 6에 나와 있습니다. 보드는 수직 방향으로 배치되어 있고 트레이스는 하단 레이어에 있으며 접지선은 상단 레이어에 연결되어 있습니다. PCB와 Ground 사이에는 로컬 접지 연결이 없습니다.

노이즈 소스 및 종단

트레이스는 버퍼 또는 마이크로 컨트롤러에서 나오는 신호에 의해 여기되고 고정 임피던스에 의해 종단됩니다. 이는 일부 고주파 성분이 있는 클록 또는 통신 신호를 모델링합니다. Simulation에서 여기는 100kHz ~ 300MHz 주파수 범위의 광대역 전압 소스입니다. 종단은 50kΩ 저항입니다. 테스트된 주파수 범위와 관련하여 종단 임피던스의 정확한 값은 중요하지 않지만 용량성 결합을 더 우세하게 만들기에 충분히 높습니다.

Simulation 방법

3D Simulation에는 Frequency Domain(FD) solver가 사용됩니다. 100kHz ~ 200MHz의 주파수 범위에서 PCB를 분석하는 데 가장 적합한 선택입니다. 먼저 FD solver를 사용하여 3D 모델을 구축, 메시화 및 해석합니다. 그런 다음, 3D Simulation 결과를 기반으로 회로 Simulation을 수행하기 위해 CST Studio Suite의 회로도와 공동 Simulation을 사용합니다.

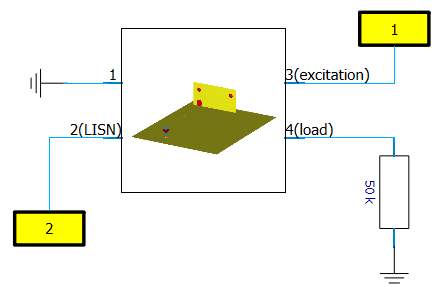

구성은 분석하고자 하는 각 포트에 연결된 임피던스와 구성 요소 측면에서 별도로 정의됩니다. 즉, 매번 3D 모델을 다시 풀지 않고도 종단 및 구동 값을 변경하고 LISN 전압을 얻을 수 있습니다. 따라서 Simulation 시간이 크게 단축됩니다. 또한 공동 Simulation 설계 흐름에서 '결과 결합' 기능을 사용하여 모든 구동 및 종단 회로를 고려하여 3D 모델에서 전류 및 EM 필드를 계산할 수 있습니다. 이 시각화는 조사에 유용합니다. Simulation 된 모든 구성에 대한 결합 프로세스를 심층적으로 분석할 수 있습니다. 테스트된 회로는 간단하며 그림 7에 설명되어 있습니다.

Simulation Case에서는 GND 와이어가 PCB에 직접 연결되었지만, 많은 설계에서 그렇듯이 “Common mode choke”"와 같은 임피던스를 통해 분리하거나 연결할 수 있다는 점에 유의하세요.

Simulation Results

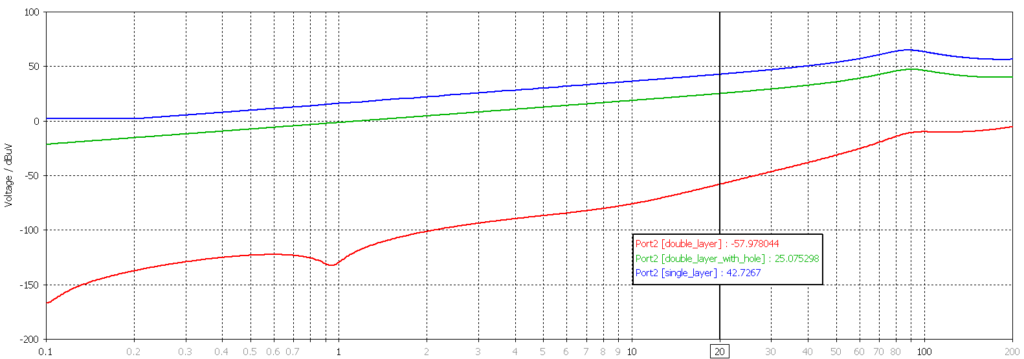

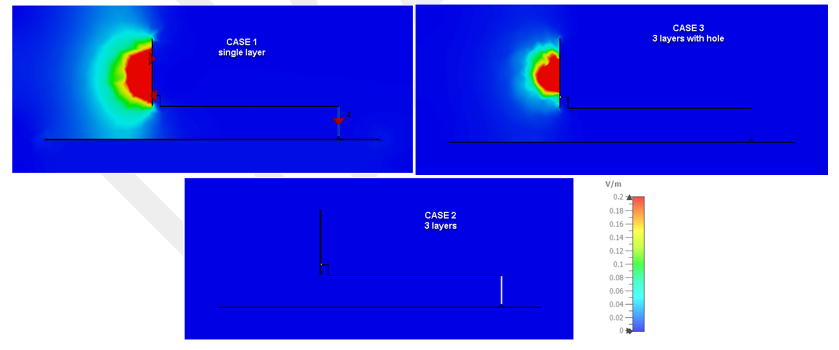

AC 분석을 사용하여 트레이스가 1V 광대역 노이즈 소스에 의해 여기되었을 때 LISN의 전압을 분석합니다. 얻은 결과는 그림 8에 나와 있습니다. Case 1 "단일 레이어"의 경우 커플링 비율이 78dB이므로 트레이스에 1V를 인가하면 20MHz에서 42dBµV가 발생하며, 이는 CISPR 25 Conducted emission 클래스 5 "협대역 잡음"의 요구 사항보다 높다는 것을 의미합니다. Case 2 "이중 레이어"의 경우 -58dBµV로 감소하며, 이는 매우 낮은 수준입니다. Case 3 "구멍이 있는 트레이스"의 경우 결합 레벨은 25dBµV이며, 이는 Case 2에 비해 83dB 증가한 수치입니다. 실제로 Case 3은 CISPR 25 클래스 5에 따라 Conducted emission의 위험이 높습니다. 전체 결과는 트레이스 위 또는 아래에 있는 접지층에 구멍이 있으면 3~4개의 레이어를 사용하여 얻은 개선 효과를 82dB(-58dBµV에서 25dBµV로) 감소시키는데, 이는 3D Simulation을 사용하지 않으면 추론하기 매우 어려운 수치입니다.

커플링 메커니즘 분석하기

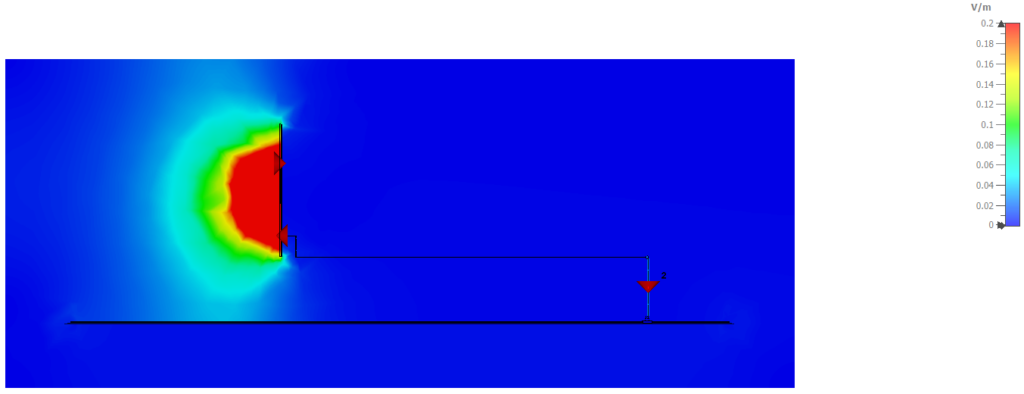

이 시점에서 가장 먼저 떠오르는 질문은 다음과 같습니다: PCB와 Ground 사이에 연결이 하나만 있는데 어떻게 LISN에 전류가 흐를 수 있을까요? 이 질문에 답하기 위해 20MHz에서 E 필드 모니터를 사용할 수 있습니다(그림 9 참조). PCB와 Ground 사이에 전기장이 존재한다는 것을 명확하게 알 수 있습니다. 이 필드의 변화는 그림 10에 표시된 것처럼 PCB와 Ground 사이의 부유 커패시턴스를 통해 변위 전류를 유도합니다. 이 변위 전류는 LISN 임피던스에 전압을 유도합니다.

Case 2와 같이 트레이스가 두 접지층 사이에 매립되면 트레이스와 Ground 사이의 커플링이 크게 감소합니다. 실제로 트레이스와 접지 층 사이의 결합이 크게 증가하여 전류 분포가 내부 레이어 사이에 국한되도록 변경됩니다. 전기장이 트레이스 층과 PCB 층 사이에 국한되므로 PCB 층의 외부 면에는 전류가 흐르지 않고 PCB 층과 Ground 사이에는 전계가 존재하지 않습니다. 이는 PCB와 Ground 사이의 결합을 감소시킵니다.

"Case 3"에서와 같이 PCB 레이어에 트레이스 위에 구멍이 있는 경우, 커플링 레벨은 Case 1 "단일 레이어" 그림 12의 레벨에 가까워집니다. 그 차이는 33dB에 불과합니다. 물론 이 값은 구멍의 위치와 크기에 따라 달라집니다.

결론

3D Simulation을 사용하여 Conducted emission 테스트 설정에서 PCB와 Ground 사이의 결합을 테스트했습니다. 그 결과 높은 임피던스로 종단된 트레이스는 트레이스와 Ground 사이에 전기장을 생성하여 LISN 임피던스에서 변위 전류와 전압을 유도하는 것으로 나타났습니다. 트레이스가 두 개의 내부 레이어 사이에 라우팅되면 이러한 커플링이 크게 감소합니다. 그러나 트레이스 위나 아래에 접지층 중 하나에 구멍이 있으면 이러한 개선 효과가 크게 저하될 수 있습니다. PCB의 짧은 부분 위에 작은 구멍만 있어도 개선 효과가 크게 저하될 수 있다는 놀라운 결론이 나왔습니다. 제안된 Simulation 워크플로우를 사용하면 구동 및 종단 임피던스를 변경하거나 PCB 레이아웃을 수정하는 등의 방법으로 대체 구성을 테스트하는 것이 매우 간단합니다.

본 자료는 다쏘시스템의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : EMC Simulation of the Coupling Between a PCB and a Ground Plane (다쏘시스템, Djamel Guezgouz)