[문서] Jitter Compliance of SerDes Channels 관리자 | 2021.10.22 | 조회 933 첨부파일 :

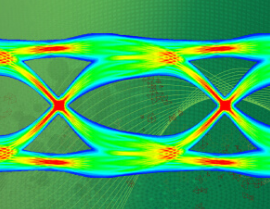

SerDes 채널에 대한 데이터 속도가 계속 증가함에 따라, 신호 무결성(SI : Signal Integrity)은 설계 프로세스에서 점점 더 중요해지고 있습니다. 패시브 채널에서 좋은 S-Parameter(예: 낮은 삽입 손실)가졌다고 해서 신호가 좋은 타이밍을 갖는지 또는 지터 컴플라이언스 테스트를 통과하는지 확인할 수 없습니다. jitter budget은 대개 낮은 비트 오류율로 정의되며, 시뮬레이션과 측정 모두 이 낮은 비트 전송률에서 jitter를 얻기가 어렵습니다. CST Studio Suite은 매우 사용하기 위훈 GUI환경 내에서 타이밍 분석(예: 데이터 독립 지터의 동일화, 인코딩 및 계산)을 위한 Eye-diagram 후처리 기능을 제공하고 있기 때문에 엔지니어가 효율적으로 지터를 분석할 수 있게 해줍니다. 사용되는 통계적 방법은 매우 낮은 비트 오류율의 지터를 빠르고 정확하게 추정할 수 있습니다.

본 E-seminar에서는 다음과 같은 항목을 확인 가능합니다

1. 시뮬레이션 및 측정에 사용되는 지터 계산 방법론. 2. 복잡한 SerDes 채널을 3D로 시뮬레이션하고 UBS 3.1 Type C 커넥터의 예와 함께 Eye Diagram 도구를 사용하여 지터 분석을 수행하는 방법.

■ 자세한 내용 및 해석 사례는 다쏘시스템즈 홈페이지에서 확인 가능합니다.