[문서] Extracting (partial) Inductance, Capacitance and Resistance from Electromagnetic Simulation 관리자 | 2023.04.25 | 조회 481 첨부파일 :

루프 및 Partial 인덕턴스의 개념과 전자기 시뮬레이션에서 RLC 모델을 추출하는 방법에 대해 설명합니다.

CST Studio Suite의 새로운 RLC solver가 Partial RLC 모델의 시뮬레이션을 어떻게 개선하는지 살펴보고 본드 와이어가 있는 패키지 모델에 대한 RLC solver의 해석 모델도 살펴보도록 하겠습니다.

전자기 시뮬레이션에서 (partial) 인덕턴스, 커패시턴스 및 저항 추출

Dassault Systèmes, Andreas Barchanski

전자계 시뮬레이션에서 등가 모델을 추출하는 아이디어는 전자기장 시뮬레이션 자체만큼이나 오래되었습니다. 물리적 구조의 특성을 그 거동을 적절히 모사할 수 있는 등가모델로 변환할 경우 시스템 또는 회로(SPICE) 시뮬레이션과 같은 추가 처리에 이러한 모델을 사용할 수 있습니다. 이러한 등가모델을 모사하여 해석에 사용하는 대표적인 예로는 고전력 부품을 연결하는 버스 바, PCB의 신호 trace, 고속 채널의 긴 비아 또는 패키지의 본드 와이어 등이 있습니다. 모든 전기 엔지니어라면 저항, 인덕턴스, 커패시턴스(RLC)로 구성된 Lumped network로 변환된 등가회로를 매우 자연스럽게 사용가능합니다. 이러한 접근 방식은 구조 크기가 관심 주파수의 파장의10분의 1보다 작은 경우 잘 동작됩니다.

전자파 적합성(EMC) 및 전자 설계 자동화(EDA) 애플리케이션에서 구조의 인덕턴스는 kHz 범위 이상의 주파수에서 전체 임피던스의 지배 인자가 되므로 특히 중요합니다. 대partial의 전기 엔지니어는 인덕턴스라는 용어를 들으면 즉시 신호 링잉에 대해 생각할 것입니다. 따라서 오늘의 포스팅에서는 전자기장 시뮬레이션을 통한 인덕턴스 계산에 대해 좀 더 자세히 살펴보겠습니다.

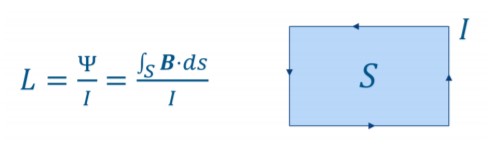

전통적으로 인덕턴스는 라인 전류 𝐼로 둘러싸인 표면 S를 통과하는 자속으로 정의됩니다. 자속은 표면을 적분하여 B에서 계산할 수 있으므로 다음과 같이 구할 수 있습니다:

표면을 정의하려면 항상 폐쇄 루프가 필요하기 때문에 이를 루프 인덕턴스라고 합니다. Fullwave solver에서 폐쇄 루프 인덕턴스를 추정하는 것은 매우 간단합니다. 해석을 위해 S-parameter port에 의해 닫힌 전도성 루프를 정의합니다. 템플릿 기반 후처리를 사용하여 S-parameter를 Z-parameter로 변환하거나 직접 인덕턴스로 변환합니다. 동일한 단계를 통해 루프의 저항도 계산할 수 있습니다. 루프 인덕턴스는 전류가 항상 루프에서 흐르기 때문에 시스템의 물리적 동작과 밀접한 관련이 있습니다. 그러나 전자 설계자에게 반드시 가장 적절한 결과는 아닙니다.

최신 전자 시스템에서 전체 전류 루프는 여러 PCB, 케이블 및 커넥터를 통해 흐르는 기하학적으로 매우 복잡할 수 있습니다. 설계자는 종종 전류 루프의 특정 섹션이 전체 인덕턴스에 어떻게 기여하는지에 관심이 있습니다. 이것이 partial 인덕턴스 개념의 출발점입니다. 전류의 일부 구간(예: 위 그림에서 직사각형의 아래쪽 구간)에서만 기여도를 계산하려는 경우 더 이상 폐쇄 루프가 없으므로 위의 공식을 사용할 수 없습니다. B와 같은 전계량을 계산하는 대신 우회하여 𝑩 = 𝛻 × 𝑨로 자기장과 관련된 적절하게 선택된 벡터 전위 A를 계산해야 합니다. 본 포스팅을 통해 모두 소개하기 어려운 자기장 이론이 이를 설명하는데 포함되나 자세한 내용은 다루지 않겠습니다. 이 계산은 "표준" Fullwave solver로는 수행할 수 없으며 특수한 solver가 필요하다는 것입니다.

전통적으로 partial 인덕턴스 계산은 PEEC(partial mesh 등가 회로 방법)라는 수치적 방법으로 이어집니다. 이 방법은 모멘트 방법(MOM)과 밀접한 관련이 있으며 수년 동안 partial 수량 계산에 사용되어 왔습니다. 그러나 이 방법에는 복잡한 CAD 구조에 적용하기 어려운 특수 메시가 필요하다는 단점이 있습니다. 또한 자성 재료 특성과 관련된 몇 가지 문제가 있으며 mesh element의 수에 따라 스케일이 심하게 확장됩니다.

따라서 SIMULIA는 위에서 언급한 어려움을 겪지 않는 다른 접근 방식을 사용하여 partial 추출을 처음부터 다시 생각하기로 결정했습니다. CST Studio Suite의 RLC solver는 지난 몇 년 동안 많은 애플리케이션에서 효율적인 선택으로 입증된 유한 mesh법(FEM)을 기반으로 합니다. 이 solver는 복잡한 구조 형상을 처리할 수 있으며 곡선 메시 mesh도 사용할 수 있습니다. 매우 효율적으로 확장할 수 있어 복잡한 CAD 구조를 가져온 경우에도 바로 사용할 수 있습니다. 고투자율 및 고투과성 재료를 처리할 수 있으며 근사치 없이 DC에서 고주파까지 풀 수 있습니다. 추출된 RLC 값은 직접 판독할 수 있도록 CST Studio Suite 1D results에 plot되거나 SPICE 파일로 내보낼 수 있습니다. 단일 주파수 및 광대역 내보내기가 모두 가능합니다.

partial RLC 추출의 주요 적용 분야는 일반적으로 파장보다 훨씬 작은 구조입니다: 예를 들어, 관심 주파수가 MHz 범위인 전력 전자 애플리케이션의 버스바 또는 주파수는 수 GHz일 수 있지만 본드 와이어의 길이가 다소 짧은 패키지의 본드 와이어등의 해석이 이에 해당합니다. 사람이 판독할 수 있는 RLC 값을 추출하는 것은 RLC 접근법의 매우 중요한 장점이며 구조의 동작을 이해하는 데 도움이 됩니다. 이 방법은 mesh 수가 많은 시스템을 판독하고 해석하는 것이 점점 더 어려워지기 때문에 구성 mesh 수가 적은 모델에 가장 효과적입니다. 블랙박스 유형의 모델이 필요한 시스템 레벨 시뮬레이션의 경우 일반적으로 Fullwave solver와 S parameter를 사용하는 것이 좋습니다. 필요한 경우 벡터 피팅을 사용하여 S parameter를 SPICE 모델로 변환할 수 있습니다.

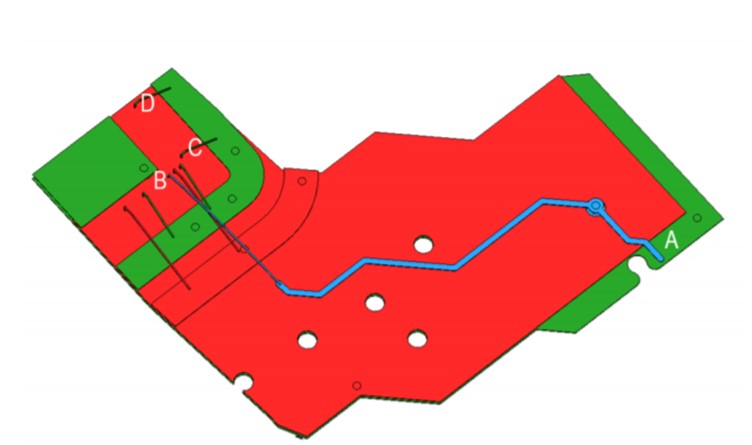

아래 예제에서는 팬 아웃 trace가 있는 패키지 본드 와이어의 인덕턴스 추출을 살펴보겠습니다. 이 패키지는 최첨단 패키지 설계 소프트웨어를 사용하여 설계되었습니다. 이 설계는 사용자가 가져올 패키지의 네트와 섹션을 추가로 선택할 수 있는 강력한 built-in import인터페이스를 사용하여 CST Studio Suite로 직접 가져왔습니다. 보다 명확한 이해를 위해 모델에 색을 입혔습니다: 관심 네트 B_DQ_14는 파란색, VCC는 빨간색, GND는 녹색입니다. 기판은 시뮬레이션에 포함되지만 아래 그림에서는 숨겨져 있습니다.

partial 인덕턴스의 경우 A 지점에서 B 지점까지의 경로를 패키지 연결의 인덕턴스로 정의하는 것은 매우 간단합니다. 그러나 루프 인덕턴스의 경우 칩 내부의 실제 라우팅에 따라 전류 루프가 닫힐 가능성이 여러 가지 있습니다. 실제 칩에서 패키지의 속성을 분리하려는 경우 partial 추출을 통해서만 가능합니다. 그래도 결과를 살펴보고 partial 인덕턴스, partial 접근법을 사용하여 계산된 루프 인덕턴스 및 전파 솔버를 사용하여 계산된 루프 인덕턴스를 비교하는 것은 가치가 있습니다. 데모 목적으로 본드 와이어 C와 D를 선택했습니다. 루프를 닫기 위해 B에서 C로, B에서 D로 각각 금속 연결을 추가합니다.

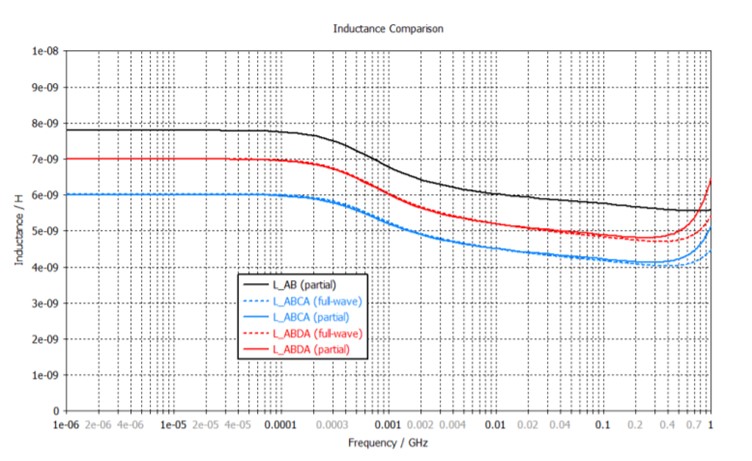

인텔 i7-7820HQ 프로세서가 장착된 노트북에서 partial RLC 솔버의 경우 약 7분, 전파 솔버의 경우 약 15분 정도 시뮬레이션이 소요됩니다. 다양한 경우의 인덕턴스는 위 그림에 표시되어 있습니다. 일반적인 동작을 관찰할 수 있습니다: 100kHz 이하에서는 인덕턴스 값이 가장 높으며, 이 영역을 종종 DC 인덕턴스라고 합니다. 1MHz 주변에서는 skin effect 효과로 인해 감소하고 100MHz 주변에서는 소위 AC 인덕턴스가 있습니다. 대partial의 경우 이 두 영역은 예제에서보다 훨씬 더 평평합니다. 이 예에서는 패키지 모델의 도체 치수가 작기 때문에 DC에서 AC로의 전환 범위가 매우 넓습니다. 1GHz 부근에서 값의 증가를 관찰할 수 있습니다. 이 주파수는 파장 대비 루프의 전기적 길이가 약 𝜆/10이 되는 주파수이며, 더 이상 단일 인덕턴스 값을 사용하여 루프의 전기적 특성을 정확하게 설명할 수 없습니다. partial 인덕턴스 AB는 루프 인덕턴스 ABCA 및 ABDA보다 높습니다. 이는 전체 루프가 포함될 때 리턴 전류가 결과 인덕턴스를 감소시키기 때문에 일반적인 결과입니다.

저항을 계산할 때는 인덕턴스와 정확히 동일한 접근 방식을 사용할 수 있습니다. 그러나 커패시턴스의 경우 정전기 시뮬레이션과 매우 유사한 다른 단계를 해결해야 합니다. partial 커패시턴스의 개념은 물리적인 해석이 부족하기 때문에 혼란스러울 수 있습니다. 커패시턴스는 전도체의 속성이므로 두 개의 전도체는 하나의 커패시턴스 값(자체 커패시턴스 생략)으로 설명할 수 있습니다. 그러나 partial 인덕턴스 계산에 필요한 것처럼 하나의 도체에 여러 노드가 정의되어 있는 경우, 예를 들어 SPICE 내보내기와 같은 일관된 모델을 생성하려면 전도체의 커패시턴스를 이러한 노드에 분산시켜야 합니다. 이것이 partial 커패시턴스 개념의 배경이 되는 아이디어입니다.

이 블로그 게시물에서는 전자기 시뮬레이션을 통해 RLC 값을 추출하는 몇 가지 주요 아이디어를 설명하려고 노력했습니다. 기억해야 할 핵심 사항은 다음과 같습니다:

- 단일 RLC 값은 전기적으로 작은 구조의 특성을 설명하는 데 사용할 수 있습니다.

- 루프 인덕턴스는 물리적으로 중요하지만, partial 인덕턴스를 추출하면 구조의 분리된 섹션의 기여도를 추정할 수 있으므로 전자 제품 설계자에게 매우 유용할 수 있습니다.

- frequency dependent 인덕턴스는 일반적으로 DC 및 AC 인덕턴스라고 하는 두 개의 영역을 나타냅니다.

- partial 커패시턴스 개념은 하나의 전도체에서 여러 노드에 커패시턴스를 분배하는 데 사용됩니다.

저자 : Andreas Barchanski

Andreas is a senior solution consultant for electromagnetic simulation at Dassault Systèmes in Darmstadt, Germany. After receiving his PhD in numerical electromagnetics from the Darmstadt University of Technology in 2007 he joined CST which later became a part of Dassault Systèmes. His main interest lies in the simulation of electromagnetic compatibility of electronic systems, ranging from high-speed to power electronics.

- 본 자료는 다쏘시스템 코리아 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

- 원본 : 다쏘시스템코리아 블로그