[문서] CST Studio Suite을 이용한 고속 Backplane simulation 관리자 | 2023.05.22 | 조회 474 첨부파일 :

본 게시물에서는 SIMULIA의 진정한 Transient EM/Circuit Co-Simulation을 사용하여 신뢰할 수 있는 Backplane을 설계하는 방법을 보여드리고자 합니다. 실제 프로토타입을 테스트하지 않고도 simulation에서 KPI 및 성능 지수(예: eye 다이어그램)를 계산하는 방법을 보여주고, Macro 모델 Circuit simulation 방법에 비해 Transient Co-simulation(tran-co)의 이점을 소개합니다.

IBIS-AMI를 사용한 Backplane 모델링 소개

긴 도달 거리의 Backplane 설계는 까다로운 작업입니다. 일반적으로 데이터 속도는 최대 수십 기가비트이고 채널 길이는 약 1미터입니다. loss tangent = 0.02인 FR4와 같은 기존 유전체는 이렇게 긴 채널에서 상당한 삽입 손실(IL)을 초래합니다. IL을 완화하려면 손실이 낮은 새로운 재료가 필요합니다. 송신기, 수신기 및 커넥터의 라인 임피던스는 낮은 반사 손실(RL)을 달성하기 위해 일치해야 합니다.

입출력 buffer 정보 사양(IBIS)[1]은 입출력(I/O) buffer 모델링을 위해 업계에서 널리 사용되고 있습니다. IBIS 알고리즘 모델링 인터페이스(IBIS-AMI)[1]를 사용하면 Serializer/Deserializer (SerDes) PHY의 필수 부분인 공급업체별 이퀄라이제이션 및 클록 복구 알고리즘을 사용할 수 있습니다. AMI simulation의 첫 번째 단계는 passive 채널 및 I/O buffer 모델의 임펄스 response을 구하는 것으로, 이는 Step response의 미분과 동일합니다.

진정한 Transient EM/Circuit Co-simulation

기존 workflow에서는 passive 채널의 산란 파라미터(S-parameter)를 먼저 계산한 다음 표준 macro 모델링을 통해 SPICE 모델로 변환합니다. 결국 SPICE 모델을 simulation하여 Step response을 얻습니다.

기존 Workflow와 비교하여 새로운 Transient EM/Circuit Co-simulation(tran-co) 방법[2]을 도입하여 S-parameter와 macro 모델을 사용하지 않고 Step response을 계산하며, 이는 시간 영역에서 맥스웰 방정식과 Circuit 요소(예: IBIS 모델 또는 AC 커플링 커패시터)를 함께 풀 수 있습니다. 기존 workflow보다 더 빠르며 비물리적 동작을 피할 수도 있습니다.

Backplane passive 채널의 삽입 손실

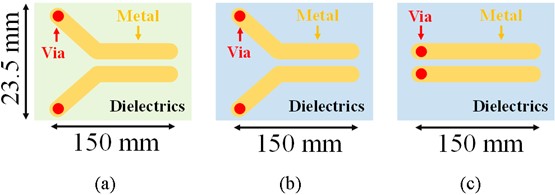

1미터 길이의 passive 채널을 설계하기 전에 더 짧은 테스트 보드 세 개를 테스트합니다.

A. 테스트 보드 A: 손실 탄젠트 = 0.02, 유전율 = 4.2, 불일치 임피던스의 유전체,

B. 테스트 보드 B: 손실 탄젠트 = 0.008, 유전율 = 3.2, 불일치 임피던스의 유전체,

C. 테스트 보드 C: 손실 탄젠트 = 0.008, 유전율 = 3.2, 송신기와 수신기에서 100Ω의 일치하는 Differential 임피던스를 가진 유전체.

그림 1. 금속 재료와 동일한 크기와 구리를 사용한 세 개의 테스트 보드 A, B, C

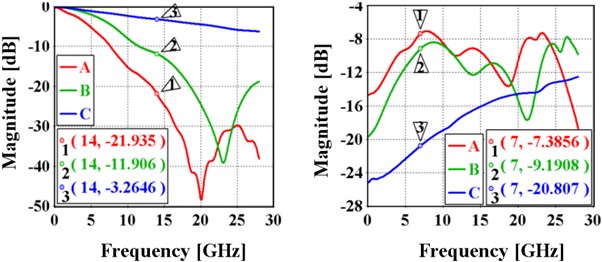

simulation 결과는 다음 그림에 요약되어 있습니다. 다음 왼쪽 그림에서 곡선 A와 B의 SDD21을 비교하면 유전체 손실이 삽입 손실에 미치는 영향을 관찰할 수 있습니다. 1m 길이 채널의 경우 손실 탄젠트 = 0.02인 FR4와 같은 일반적인 유전체는 상당한 삽입 손실을 초래하며, 150mm 채널의 경우 이미 -12dB로 떨어집니다. 따라서 손실이 낮은 신소재가 선호됩니다. 오른쪽 그림에서 B와 C의 SDD11 곡선을 비교하면 특히 differential pairs의 단면이 크게 변할 수 있는 비아와 커넥터에서 임피던스를 일치시키는 것이 중요하다는 것을 알 수 있습니다.

그림 2. 테스트 보드 A, B, C의 simulation 결과(왼쪽: SDD21, 오른쪽: SDD11)

SerDes Step response의 macro 모델

다음에서는 IBIS Tx/Rx buffer 모델, AC 커플링 커패시터 및 3D passive 채널이 포함된 SerDes 채널의 Step response을 계산합니다.

그림 3. 전체 simulation 네트워크에는 3D 모델과 Circuit 요소가 포함

3D passive 채널의 S-parameter를 먼저 계산한 다음 macro 모델로 변환하여 time domain에서 Circuit 요소(예: IBIS 모델 및 AC 커플링 커패시터)와 함께 simulation하여 Step response을 얻을 수 있습니다. 이 블로그에서는 이 workflow를 기존 또는 Circuit workflow라고 합니다. 그러나 긴 passive 채널(예: 최대 simulation 주파수 λ의 자유 공간 파장이 수십 λ인 경우)의 경우 S-parameter 계산에 많은 시간이 소요될 수 있으며 기존 macro 모델링 프로세스는 비효율성(최종 Circuit의 크기가 크기 때문에)과 시스템 레벨 simulation의 정확도 저하(전파 지연의 부정확한 모델링으로 인해)를 초래할 수 있습니다. 이러한 이유로 본 논문에서는 S-parameter나 macro 모델을 계산할 필요 없이 3D passive 채널과 Circuit 소자를 시간 영역에서 단계적으로 함께 풀어서 step response을 구하는 Tran-co Workflow[2]를 소개합니다. Circuit와 Tran-co Workflow를 테스트 보드 C에 적용하여 그 성능을 다음 표에 요약했습니다.

Table Ⅰ. Simulation statistics of Test board C

Max. Freq. Board Length Mesh Cells Circuit Tran-co

112 GHz 150 mm ≈ 56 λ 68,186,250, 117 min 86 min

위 표에서 볼 수 있듯이 Tran-co Workflow 해석 결과로 simulation은 CPU @2.0GHz, GPU 2xKepler Tesla K40c+m, 256GB RAM이 장착된 머신에서 실행되었습니다.

Transient co-simulation과 macro 모델 Circuit simulation 비교

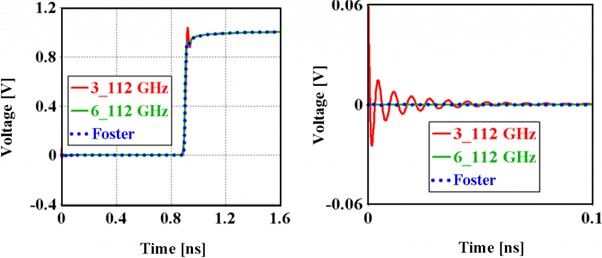

Tran-co Workflow의 Step response을 Circuit solver[3]에서 residues-poles형태(Foster Pole-Residue [2])를 사용하여 합성한 macro모델을 simulation하여 얻은 결과와 비교합니다. 아래 그림과 같이 덩어리 소자로 합성된 macro모델을 사용하면 Step response의 시작 부분에서 비물리적 ripple이 나타납니다(빨간색, 3_112GHz). 그러나 Tran-co Workflow(녹색, 6_112GHz)와 Circuit Workflow의 poles/residues macro모델(파란색, 포스터)의 결과는 서로 일치하며 비물리적인 거동을 피할 수 있습니다.

그림 4. step response(a)과 t = 0 주변 확대 보기(b)의 비교

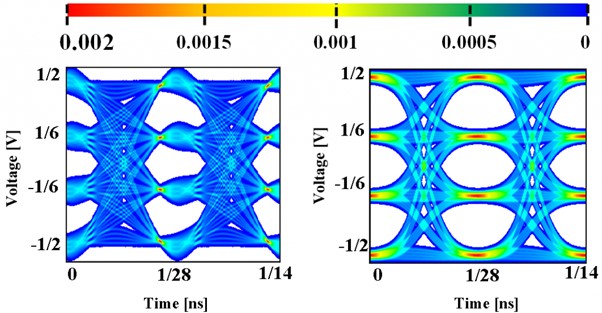

Circuit 및 Tran-co Workflow에 대한 통계적 Eye diagram이 생성됩니다. macro 모델이 덩어리 요소로 합성된 Circuit Workflow의 Eye diagram은 아래 왼쪽 그림과 같이 변형된 것을 확인할 수 있습니다. 아래 오른쪽 그림은 Tran-Co Simulation Workflow의 Eye diagram입니다.

그림 5. Circuit(a) 및 Tran-co(b) Workflow의 통계적 Eye diagram

Full 3D Backplane 채널 simulation

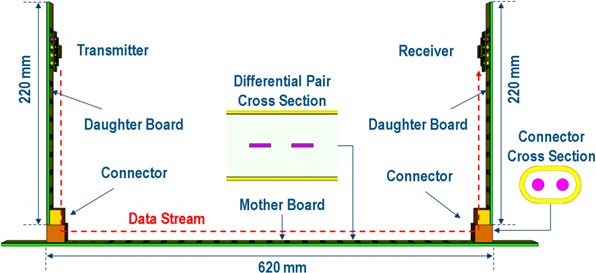

마지막으로 다음 그림과 같이 Tran-co Workflow를 따라 Backplane에서 1미터 길이의 채널을 simulation합니다. 전송 라인과 커넥터의 Differential 임피던스는 100옴으로 최적화되어 있습니다. 기판에는 유전율이 3.2인 무손실 유전체가 사용됩니다.

그림 6. Backplane의 완전한 3D passive 채널

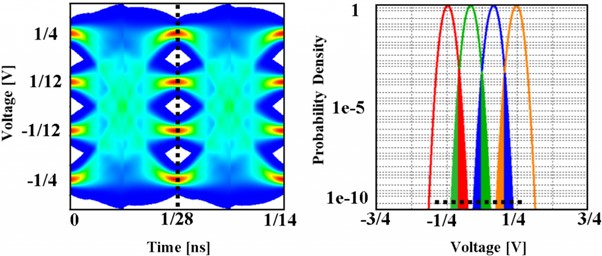

Step response을 얻은 후 사전 탭 1개와 사후 탭 2개가 있는 3-taps-FFE(Feedforward Equalizer)와 3-taps-DFE (Decision Feedback Equalizer)를 사용하여 무작위 jitter를 포함하지 않는 통계적 Eye diagram을 개선합니다. 따라서 각 레벨의 확률 밀도(PD)에는 결정론적 jitter만 포함됩니다. Eye diagram의 결정적 jitter를 무작위 잡음으로 컨볼루션하여 아래와 같이 신호 대 잡음비(SNR)가 12dB인 PD를 얻습니다.

그림 7. Eye diagram의 점선으로 표시된 통계적 Eye diagram 및 전압 확률 밀도

Backplane simulation workflow 개요

SerDes simulation을 위한 SIMULIA CST 솔루션은 다음 그림에 요약되어 있습니다.

그림 8. SIMULIA CST SerDes 솔루션

GPU 가속 기능이 있는 CST Studio Suite® Time domain solver[2]는 SerDes 채널의 전기 대형 passive 인터커넥트를 효율적으로 simulation할 수 있습니다. IBIS-AMI [1] 및 HSPICE [3] simulation은 CST Design Studi에서 실행할 수 있습니다. version 2022에서는 컴포넌트 라이브러리에 IBIS-AMI 데모가 추가되어 사용자가 IBIS-AMI simulation을 원활하게 시작할 수 있습니다. CST Studio Suite® IDEM [2]은 S-parameter를 SPICE 모델로 변환하는 최첨단 macro 모델링 기법을 제공합니다. Eye diagram 툴을 사용하면 일반적인 SerDes 기술(예: 이퀄라이제이션 또는 4레벨 펄스 진폭 변조(PAM4))을 passive 채널 설계에 적용할 수도 있습니다. Eye diagram 툴은 사용자 정의 RJ(랜덤 jitter) 및 통계적 Eye diagram을 지원합니다. 마지막으로 simulation 결과(예: Differential S-parameter 또는 확률 밀도 함수)는 CST 및 Python의 VBA macro 편집기를 통해 쉽게 액세스할 수 있습니다. 따라서 사용자는 IBIS-AMI 표준[1]에서 지원하지 않는 Channel Operating Margin(COM)[4], Error Propagation(EP) 및 Forward Error Correction (FEC)과 같은 추가 분석을 VBA 및 Python 스크립트를 사용하여 수행할 수 있습니다.

References

1. IBIS Open Forum, https://ibis.org/.

2. Dassault Systèmes, https://www.3ds.com/simulia/

3. Synopsys Inc. https://www.synopsys.com/

4. IEEE Std. 802.3bj-2014.

저자 : Andreas Barchanski

Longfei Bai joined SIMULIA CST, Dassault Systèmes in 2015 as an application engineer supporting customers with EDA. He completed his B.S. from the University of Electronic Science and Technology of China in 2011 and M.S. degrees from Technische Universität Darmstadt in 2015 in the field of electrotechnics. His primary focus now is on SI, PI and EMC on PCB, package and chip.

본 자료는 다쏘시스템 코리아 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

- 원본 : 다쏘시스템코리아 블로그