[문서] PCB Design Rule Checking을 위한 CST BOARDCHECK 관리자 | 2023.05.31 | 조회 459 첨부파일 :

최근 고객들의 니즈에 의해 많은 전자 제품의 소형화 및 신호 고속화가 진행되고 있습니다. 그로 인해 PCB (Printed Circuit Board)가 더욱 더 집적화 되고 다양한 전자 회로 간의 전자기 노이즈가 발생할 확률 또한 증가하는 추세입니다.

따라서 이러한 전자기 노이즈에 대한 현상을 분석하는 EMC (Electro Magnetic Compatibility) 해석 뿐만 아니라 입력단에서 인가된 신호와 전원이 출력단까지 잘 전달되는지 확인하기 위한 SI (Signal Integrity, 신호 무결성) 및 PI (Power Integrity, 전원 무결성) 해석에 대한 요구가 늘어나고 있습니다. PCB 해석에서 발생할 수 있는 이러한 EMC, SI, PI 적인 문제는 CST에서 제공하는 BOARDCHECK® 기능을 이용하여 빠른 탐색을 해볼 수 있습니다.

본 포스팅에서 CST BOARDCHECK® 기능에 대해 소개하고 어떠한 분석들을 진행할 수 있는지에 대해 소개해 드리도록 하겠습니다.

전자기기의 소형화, 그리고 빠른 속도의 통신을 위한 신호의 고속화로 인해 Printed Circuit Board (PCB)는 더욱 집적화 되었고, 많은 전자기 노이즈 성분들이 발생하게 됩니다. 복잡한 PCB에서 신호와 전원이 배선을 통해 설계자가 의도한 대로 잘 전달이 되는지를 확인하는 신호 무결성(SI-Signal Integrity) / 전원 무결성 (PI-Power Integrity)에 대한 분석이 필수적으로 필요하게 되었고, 전자기기 간의 상호 전자기 노이즈 영향에 대한 시험 분석인 전자파 적합성 (EMC–ElectroMagnetic Compatibility)의 분석에 대한 요구가 점점 늘어나고 있습니다.

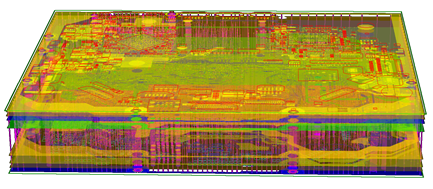

하지만 앞서 언급한 것 같이 PCB는 더욱 복잡해지고 수 백, 수 천 개의 배선과 소자들, 그리고 많은 층으로 이루어진 구조로 인해 PCB의 어느 부분에서 문제가 발생하는지를 예측하고, 파악하는 것은 더욱 어려운 문제가 되었습니다.

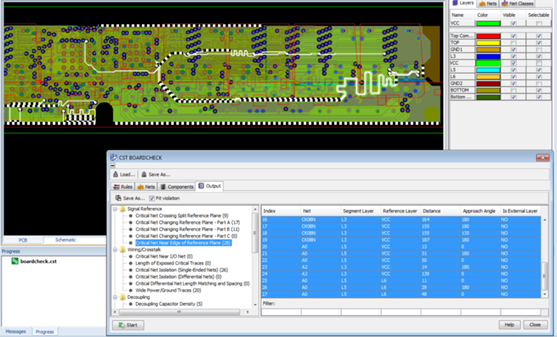

그림1. 다양한 Net, Component, Layer로 구성된 PCB 구조

이러한 분석에 CST에서 제공하는 여러 제품 중 CST BOARDCHECK®을 이용하게 되면 SI/PI/ EMC적으로 문제가 발생할 수 있는 부분에 대한 빠른 탐색이 가능합니다. 이번 블로그 포스팅에서는 CST BOARDCHECK® 기능에 대해 소개하고, 어떠한 분석들을 진행할 수 있는지에 대해 소개 드리도록 하겠습니다.

CST BOARDCHECK®란?

CST PCB STUDIO® 내에 있는 CST BOARDCHECK®은 일반적으로 잘 알려진 PCB 설계 규칙 가이드를 정규화하여 분석할 수 있도록 만들어진 PCB 설계 검증 솔루션입니다. PCB의 설계 초기 단계에서 아래의 표에서 명시한 26가지의 SI/PI/EMC 설계 가이드를 통해 문제를 일으킬 수 있는 부분을 빠르게 찾아낼 수 있으며, 이에 대한 PCB 설계 수정을 통해 전자기적 문제를 초기 단계에서 차단할 수 있도록 도움을 주는 프로그램입니다.

|

EMC Rules |

SI Rules |

PI Rules |

|

Differential Net Isolation |

Differential Net Isolation |

Decoupling Capacitor Density |

|

Differential Net Matching |

Differential Net Running Skew |

Decoupling Capacitor Distance to Via |

|

Distance from Filter to Connector |

Net Length |

IC Power/Ground Pin-Via Distance |

|

Distance from Oscillator to Clock Driver |

Net Stub |

Narrow Power/Ground Traces |

|

Exposed Trace Length |

Routing between two Reference Planes |

Power/Ground Trace Decoupling |

|

Net Changing Reference |

Single-Ended Net Isolation |

Power Net Overlapping |

|

Net Crossing Split |

Unconnected Via Pads |

Power Pin Capacitor Distance |

|

Net Near Connector Net |

Via Clearance Overlap |

Power Via Density |

|

Net Near Edge of Reference |

Via Stub |

|

|

Single-Ended Net Isolation |

Via to Net Coupling |

|

표1. 26가지의 SI/PI/EMC 영역 PCB 설계 규칙 가이드

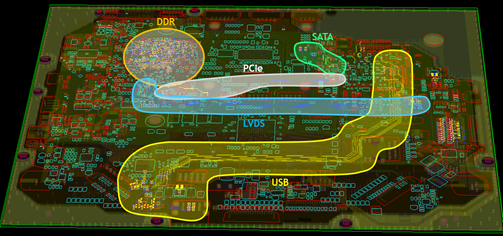

아래의 그림에서 볼 수 있듯이 PCB는 서로 다른 용도의 다양한 신호들의 집합체라 볼 수 있습니다. 그렇기 때문에 PCB에 모두 동일한 설계 규칙을 적용하여 위반사항을 찾을 경우 정확한 분석이 어려울 수 있습니다. CST BOARDCHECK®에서 제공하는 Signal Specification 기능을 통해 배선마다 사용하는 특정 신호에 대해 지정을 할 수 있으며, 지정된 특정 신호들에 따라 설계 규칙 내부의 인자들이 다르게 설정되어 위반사항을 효과적으로 검출해 줍니다.

그림2. PCB에서 사용되는 다양한 신호

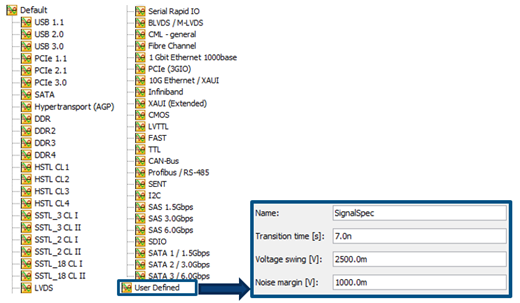

사용할 수 있는 Signal Specification 상의 신호들은 아래와 같이 USB, PCIe, DDR 등과 같은 다양한 신호들에 대한 규칙 설정을 지정할 수 있으며, 만약 사용하는 용도의 신호가 리스트 상에 없는 경우에는 “User Define”을 통해 새로운 신호를 만들고 해당 신호를 적용하여 설계 규칙 가이드 위반 사항을 검출할 수도 있습니다.

그림3. Signal Specification에서 제공하는 다양한 신호

각 배선에 대한 신호 설정 후 CST BOARDCHECK®을 이용한 분석을 진행하게 되면 선택된 규칙에 위반되는 배선 혹은 소자들이 있는지를 수 분 이내에 빠르게 찾아낼 수 있으며, 해석이 완료된 후 설계 규칙 위반 사항들에 대한 결과 리포트를 제공함으로써 PCB 상에서 SI/PI/EMC적으로 설계 규칙을 위반하는 사항들이 어느 부분인지를 직관적으로 보여주게 됩니다.

그림4. CST BOARDCHECK® 해석 후 얻을 수 있는 룰 위반 사항에 대한 결과 리포트

지금까지 CST BOARDCHECK®을 이용하여 어떠한 분석을 하는지, 어떠한 기능들을 제공하는지에 대해 설명했습니다. 이제는 예제를 통해 PCB 설계 초기 단계에서 문제를 확인하고, 이를 분석하였던 사례들에 대해 소개하겠습니다.

예제를 통한 CST BOARDCHECK® 소개

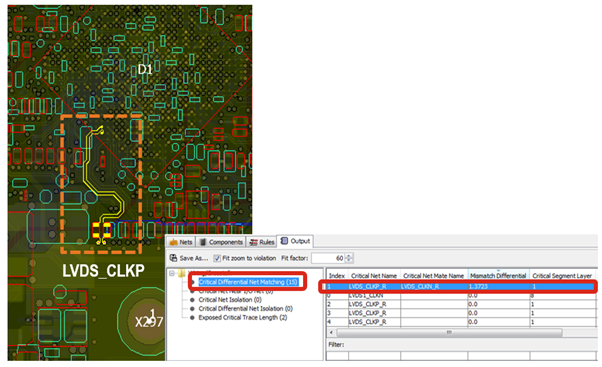

해석을 진행하게 되면 여러 설계 규칙 위반사항을 확인할 수 있었으며, 그중 “Critical Differential Net Matching”이라는 설계 규칙을 위반한 LVDS_CLK Net가 발견되었습니다. 해당 규칙의 경우 두 배선으로 이루어진 Differential Net의 길이 차가 있을 경우 공통 모드 전압이 순간적으로 크게 나타나게 되고, 이는 SI, EMC 적인 문제를 일으킬 수 있습니다. 이를 해석 결과로 보게 되면, PCB의 어느 부분에서 이러한 위반 사항이 검출되는지, 그리고 Differential Net이 얼마만큼의 길이 차이를 보이는지 등에 대한 결과를 한눈에 확인할 수 있습니다.

그림5. Critical Differential Net Matching 설계 규칙 위반 검출

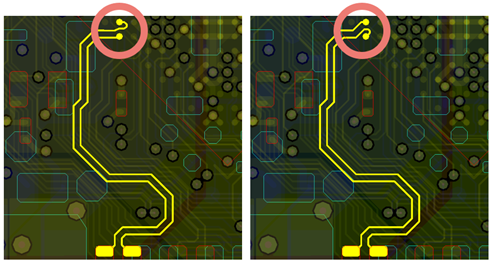

이렇게 설계 규칙을 위반한 Net가 발견되게 되면, 해당 Net를 위반 사항을 참고하여 설계 수정을 진행해 보실 수 있습니다. 해당 Differential Net의 경우 Net의 길이가 1.3723 [mm]만큼 차이가 나는 부분의 Layout을 수정하여 Net의 길이를 맞춰주는 과정을 진행하였습니다. 아래 그림의 왼쪽의 PCB에서 오른쪽의 PCB로 Net의 길이를 수정하였습니다.

그림6. 두 Differential Net 길이를 맞춰주는 과정 진행

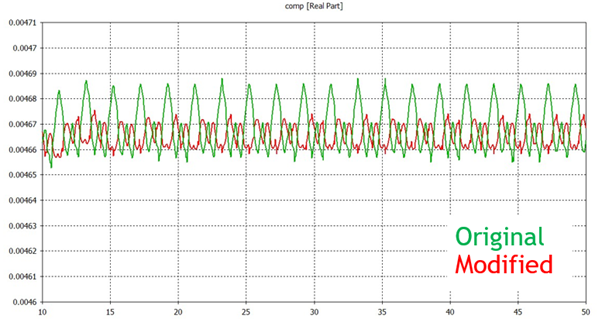

수정을 진행한 후 해당 PCB에 대한 신호 무결성 해석을 진행해 보았습니다. 아래의 결과는 Net의 길이 수정을 진행하기 전과 후의 공통 모드 전류의 결과를 확인해 본 내용으로, 초록색의 수정을 진행하기 전의 공통 모드 전류의 경우 Noise 성분의 최대치가 높게 설정되는 반면 빨간색의 수정 이후의 공통 모드 전류 결과를 보면 Noise 성분의 최대치가 많이 감소된 결과를 확인해 볼 수 있었습니다.

그림7. PCB 설계 수정 전후 신호 무결성 결과 확인

결론

다쏘시스템의 전자기장 해석 솔루션인 CST Studio Suite에는 신호 무결성과 전원 무결성에 대한 분석을 2.5D로 빠르게 진행할 수 있는 CST PCB Studio를 제공하고 있으며, 그 안에는 포스팅을 통해 설명했던 PCB에 대한 설계 규칙 가이드 위반사항을 빠르게 검출할 수 있는 CST BOARDCHECK®을 제공하고 있습니다. 또한 3D 전자기장 해석을 진행할 수 있는 CST Microwave Studio를 통해서도 PCB를 3D로 불러오기 하여 고주파 대역에서 나타나는 전자기 Coupling을 고려한 보다 정확한 신호 무결성 및 전자파 적합성 분석이 가능합니다. CST에서 제공하는 다양한 해석 제품들을 이용하여 PCB에 대한 분석을 다방면으로 분석해 보시길 바랍니다.

본 자료는 다쏘시스템의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

- 원본 : 다쏘시스템