|

|

[문서] SOC(System-on-Chip) 설계: 전자기 시뮬레이션을 통한 소스 싱크로너스 아키텍쳐 분석 및 최적화

Dassault Systèmes

Introduction 반도체 산업을 뒷받침하는 유명한 법칙인 무어의 법칙은 칩에 탑재된 트랜지스터의 밀도가 2년마다 2배씩 증가할 것이라고 예측합니다. 그러나 최근 몇 년 동안 칩 제조업체가 근본적인 물리적 한계에 다다르고 신기술 개발 비용이 급격히 증가함에 따라 무어의 법칙은 느려지고 있습니다. 대신 칩 제조업체들은 칩 성능을 향상시킬 수 있는 다른 방법을 모색하고 있습니다.

한 가지 유망한 접근 방식은 이종 집적화(Heterogeneous Integration, HI) 기술입니다. 이종 집적화는 모놀리식 실리콘 웨이퍼에 모든 기능을 구현하는 대신 각 기능에 가장 적합하고 비용 효율적인 제조 노드를 사용하여 서로 다른 기능을 서로 다른 칩에 패키징하고 이를 SoC에 통합합니다. 모듈식 칩렛은 어플리케이션의 요구 사항을 충족하도록 다양한 방식으로 결합하여 혼합 및 매칭할 수 있습니다. 모놀리식 접근 방식에 비해 이종 집적화 기술은 비용을 절감하고 제조 업체가 성능의 한계를 계속 뛰어넘을 수 있게 해줍니다.

칩렛을 연결하기 위해 소스 싱크로너스 아키텍처를 갖춘 고병렬 버스 인터페이스가 자주 사용됩니다. 이는 지연 시간을 줄이고 높은 대역폭을 유지하는 효과적인 방법입니다. 그러나 이를 구현하는 데는 여러 가지 어려움이 있습니다.

칩렛 아키텍처의 과제

이종 집적화로 설계된 SoC의 분리된 특성은 모두 연결해야 하는 개별 칩렛이 많다는 것을 의미합니다. 이러한 개별 칩렛을 연결하는데 지연 시간이 너무 길면 성능 이점을 잃게 됩니다.

일반적으로 낮은 전송 대기 시간을 달성하기 위해 HBM 및 UCIe 표준에서와 같이 소스 싱크로너스 아키텍처를 갖춘 병렬 버스가 사용됩니다. 소스 싱크로너스 아키텍처에서는 clock(스트로브)이 데이터와 함께 전용 트레이스에서 전송됩니다. 전달 시간은 트레이스 마다 다를 수 있으므로 모든 데이터 신호를 스트로브에서 올바르게 샘플링하려면 데이터 신호의 위상, 즉 skew를 일치시켜야 합니다.

데이터와 스트로브 트레이스의 skew를 일치시켜야 한다는 요구 사항은 칩렛 채널 구현에서 매우 중요합니다. 이 위상 관계를 유지하려면 데이터와 스트로브가 전파 지연을 기준으로 가능한 한 서로 일치해야 합니다.

소스 싱크로너스 아키텍처의 3D full-wave 시뮬레이션

기존의 2D 회로 시뮬레이션 방법은 밀집된 채널 간의 고밀도 수직 결합이나 도체 두께 및 저항의 영향을 포함하지 못하기 때문에 SoC에 대한 정확한 결과를 제공하지 못합니다. 아주 작은 타이밍 불일치만으로도 오류가 발생할 수 있기 때문에 데이터 속도를 GHz 단위로 측정할 수 있는 경우 이는 더욱 큰 문제입니다.

실리콘 인터포저와 TSV (Through-Silicon Vias), mesh 접지면과 같은 3D 구조도 고려해야 합니다. 실리콘 인터포저의 경우 기술 규칙 요구 사항에 따라 mesh 접지면을 사용해야 합니다. 즉, 두 신호 트레이스의 길이가 같더라도 리턴 전류의 경로가 다를 수 있으므로 총 전달 시간이 크게 달라질 수 있습니다.

2D와 3D 시뮬레이션 비교

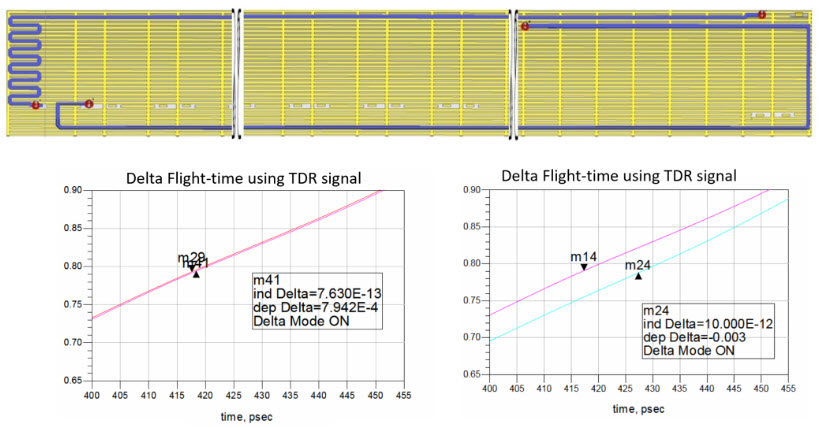

그림 1. 신호 트레이스와 시뮬레이션된 전달 시간. (왼) 2D 시뮬레이션 (우) 3D 시뮬레이션

그림 1의 시뮬레이션은 2D 시뮬레이션과 3D 시뮬레이션의 결과 차이를 보여줍니다. 동일한 구조에 대해 2D 시뮬레이션에서는 delay skew가 1초 미만으로 추정되는 반면 3D 시뮬레이션에서는 delay skew가 10초로 계산되었습니다. 2D 시뮬레이션은 회로 구성의 중요한 기여를 놓쳐서 delay skew가 10배 증가했습니다. 10Gbps 데이터 채널에서 이는 10%의 오류율에 해당합니다. 따라서 정확한 시뮬레이션이 매우 중요합니다. 그림2과 같이 시뮬레이션과 측정 간의 높은 일치도를 달성할 수 있는 시뮬레이션을 통해 엔지니어는 시뮬레이션에 대한 확신을 가질 수 있습니다.

그림 2. 데이터 Eye Width 및 Strobe-Centering 오류 상관관계

본 자료는 다쏘시스템의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템

관리자

2023.09.21

조회 488

|

|

|

[문서] 전자기 시뮬레이션을 통한 오토모티브 이더넷 설계

Dassault Systèmes

일반 자동차에 탑재되는 전자 부품의 수가 증가하고 있으며 스마트 자동차는 자동차 시장의 주요 성장 동력입니다. 전자 시스템을 개별적으로 설계하는 것은 전자 엔지니어에게 항상 어려운 과제이지만, 여러 시스템을 연결하면 또 다른 과제가 생깁니다. 빠르고 적절한 데이터 전송을 위해서는 고성능 표준에 기반한 이러한 전자 시스템 간의 통신이 핵심입니다.

예를 들어, 인포테인먼트 및 첨단 운전자 지원 시스템(ADAS)과 같은 최신 전자 시스템은 비디오 스트리밍을 위해 매우 높은 대역폭을 필요로 합니다. 컨트롤러 영역 네트워크(CAN)와 같은 기존의 차량 버스 프로토콜은 충분한 대역폭을 제공할 수 없습니다. 차량용 이더넷은 업그레이드를 위한 주요 제안 중 하나입니다.

BroadR-Reach®는 차량용 애플리케이션을 위한 지점 간 이더넷 물리 계층 표준으로, 비차폐 트위스트 와이어를 통해 두 장치 간에 100 Mb/s의 전 이중 통신을 지원하며, 최대 1000 Mb/s까지 늘릴 계획입니다. 이 높은 비트 전송률은 시스템이 고주파 간섭에 취약하다는 것을 의미하며, 1MHz 이상의 주파수에서 BroadR-Reach 오토모티브 이더넷은 CAN 버스보다 훨씬 더 높은 스펙트럼 콘텐츠를 전달합니다. 설계자는 이 점을 인지하고 이러한 높은 주파수에서 방출을 완화할 수 있는 적절한 기술을 적용해야 합니다. BroadR-Reach 이더넷이 차량용 EMC 요구 사항을 준수하도록 만드는 것은 까다로운 작업입니다.

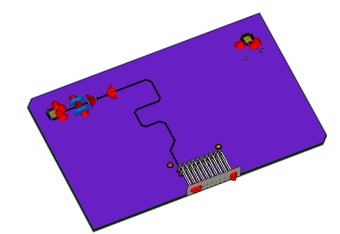

그림 1. IC, 구성 요소, 트레이스 및 커넥터를 보여주는 테스트 PCB

전통적으로 EMC 테스트는 물리적 프로토타입을 사용한 측정에 크게 의존해 왔으며, 이는 높은 수정 비용과 시장 출시 시간 지연으로 여러 번의 문제 해결 반복으로 이어질 수 있습니다. 전자기 시뮬레이션을 통한 가상 프로토타이핑을 사용하면 설계 프로세스 초기에 잠재적인 간섭 문제를 식별할 수 있어 시간과 비용을 절약할 수 있습니다. 이 백서에 제시된 예제는 모두 전파 3D 모델과 회로 시뮬레이션의 결합을 기반으로 합니다.

관련하여 자세한 내용이 궁금하신 경우 아래 링크를 통해 백서를 다운로드 받아 확인해 보실 수 있습니다.

클릭 : 다운로드

본 자료는 다쏘시스템 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템 블로그

관리자

2023.07.20

조회 326

|

|

|

[문서] PCB Design Rule Checking을 위한 CST BOARDCHECK

최근 고객들의 니즈에 의해 많은 전자 제품의 소형화 및 신호 고속화가 진행되고 있습니다. 그로 인해 PCB (Printed Circuit Board)가 더욱 더 집적화 되고 다양한 전자 회로 간의 전자기 노이즈가 발생할 확률 또한 증가하는 추세입니다.

따라서 이러한 전자기 노이즈에 대한 현상을 분석하는 EMC (Electro Magnetic Compatibility) 해석 뿐만 아니라 입력단에서 인가된 신호와 전원이 출력단까지 잘 전달되는지 확인하기 위한 SI (Signal Integrity, 신호 무결성) 및 PI (Power Integrity, 전원 무결성) 해석에 대한 요구가 늘어나고 있습니다. PCB 해석에서 발생할 수 있는 이러한 EMC, SI, PI 적인 문제는 CST에서 제공하는 BOARDCHECK® 기능을 이용하여 빠른 탐색을 해볼 수 있습니다.

본 포스팅에서 CST BOARDCHECK® 기능에 대해 소개하고 어떠한 분석들을 진행할 수 있는지에 대해 소개해 드리도록 하겠습니다.

전자기기의 소형화, 그리고 빠른 속도의 통신을 위한 신호의 고속화로 인해 Printed Circuit Board (PCB)는 더욱 집적화 되었고, 많은 전자기 노이즈 성분들이 발생하게 됩니다. 복잡한 PCB에서 신호와 전원이 배선을 통해 설계자가 의도한 대로 잘 전달이 되는지를 확인하는 신호 무결성(SI-Signal Integrity) / 전원 무결성 (PI-Power Integrity)에 대한 분석이 필수적으로 필요하게 되었고, 전자기기 간의 상호 전자기 노이즈 영향에 대한 시험 분석인 전자파 적합성 (EMC–ElectroMagnetic Compatibility)의 분석에 대한 요구가 점점 늘어나고 있습니다.

하지만 앞서 언급한 것 같이 PCB는 더욱 복잡해지고 수 백, 수 천 개의 배선과 소자들, 그리고 많은 층으로 이루어진 구조로 인해 PCB의 어느 부분에서 문제가 발생하는지를 예측하고, 파악하는 것은 더욱 어려운 문제가 되었습니다.

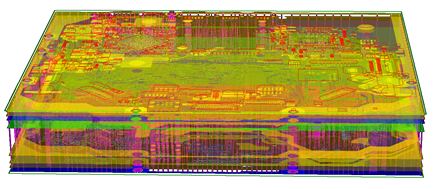

그림1. 다양한 Net, Component, Layer로 구성된 PCB 구조

이러한 분석에 CST에서 제공하는 여러 제품 중 CST BOARDCHECK®을 이용하게 되면 SI/PI/ EMC적으로 문제가 발생할 수 있는 부분에 대한 빠른 탐색이 가능합니다. 이번 블로그 포스팅에서는 CST BOARDCHECK® 기능에 대해 소개하고, 어떠한 분석들을 진행할 수 있는지에 대해 소개 드리도록 하겠습니다.

CST BOARDCHECK®란?

CST PCB STUDIO® 내에 있는 CST BOARDCHECK®은 일반적으로 잘 알려진 PCB 설계 규칙 가이드를 정규화하여 분석할 수 있도록 만들어진 PCB 설계 검증 솔루션입니다. PCB의 설계 초기 단계에서 아래의 표에서 명시한 26가지의 SI/PI/EMC 설계 가이드를 통해 문제를 일으킬 수 있는 부분을 빠르게 찾아낼 수 있으며, 이에 대한 PCB 설계 수정을 통해 전자기적 문제를 초기 단계에서 차단할 수 있도록 도움을 주는 프로그램입니다.

EMC Rules

SI Rules

PI Rules

Differential Net Isolation

Differential Net Isolation

Decoupling Capacitor Density

Differential Net Matching

Differential Net Running Skew

Decoupling Capacitor Distance to Via

Distance from Filter to Connector

Net Length

IC Power/Ground Pin-Via Distance

Distance from Oscillator to Clock Driver

Net Stub

Narrow Power/Ground Traces

Exposed Trace Length

Routing between two Reference Planes

Power/Ground Trace Decoupling

Net Changing Reference

Single-Ended Net Isolation

Power Net Overlapping

Net Crossing Split

Unconnected Via Pads

Power Pin Capacitor Distance

Net Near Connector Net

Via Clearance Overlap

Power Via Density

Net Near Edge of Reference

Via Stub

Single-Ended Net Isolation

Via to Net Coupling

표1. 26가지의 SI/PI/EMC 영역 PCB 설계 규칙 가이드

아래의 그림에서 볼 수 있듯이 PCB는 서로 다른 용도의 다양한 신호들의 집합체라 볼 수 있습니다. 그렇기 때문에 PCB에 모두 동일한 설계 규칙을 적용하여 위반사항을 찾을 경우 정확한 분석이 어려울 수 있습니다. CST BOARDCHECK®에서 제공하는 Signal Specification 기능을 통해 배선마다 사용하는 특정 신호에 대해 지정을 할 수 있으며, 지정된 특정 신호들에 따라 설계 규칙 내부의 인자들이 다르게 설정되어 위반사항을 효과적으로 검출해 줍니다.

그림2. PCB에서 사용되는 다양한 신호

사용할 수 있는 Signal Specification 상의 신호들은 아래와 같이 USB, PCIe, DDR 등과 같은 다양한 신호들에 대한 규칙 설정을 지정할 수 있으며, 만약 사용하는 용도의 신호가 리스트 상에 없는 경우에는 “User Define”을 통해 새로운 신호를 만들고 해당 신호를 적용하여 설계 규칙 가이드 위반 사항을 검출할 수도 있습니다.

그림3. Signal Specification에서 제공하는 다양한 신호

각 배선에 대한 신호 설정 후 CST BOARDCHECK®을 이용한 분석을 진행하게 되면 선택된 규칙에 위반되는 배선 혹은 소자들이 있는지를 수 분 이내에 빠르게 찾아낼 수 있으며, 해석이 완료된 후 설계 규칙 위반 사항들에 대한 결과 리포트를 제공함으로써 PCB 상에서 SI/PI/EMC적으로 설계 규칙을 위반하는 사항들이 어느 부분인지를 직관적으로 보여주게 됩니다.

그림4. CST BOARDCHECK® 해석 후 얻을 수 있는 룰 위반 사항에 대한 결과 리포트

지금까지 CST BOARDCHECK®을 이용하여 어떠한 분석을 하는지, 어떠한 기능들을 제공하는지에 대해 설명했습니다. 이제는 예제를 통해 PCB 설계 초기 단계에서 문제를 확인하고, 이를 분석하였던 사례들에 대해 소개하겠습니다.

예제를 통한 CST BOARDCHECK® 소개

해석을 진행하게 되면 여러 설계 규칙 위반사항을 확인할 수 있었으며, 그중 “Critical Differential Net Matching”이라는 설계 규칙을 위반한 LVDS_CLK Net가 발견되었습니다. 해당 규칙의 경우 두 배선으로 이루어진 Differential Net의 길이 차가 있을 경우 공통 모드 전압이 순간적으로 크게 나타나게 되고, 이는 SI, EMC 적인 문제를 일으킬 수 있습니다. 이를 해석 결과로 보게 되면, PCB의 어느 부분에서 이러한 위반 사항이 검출되는지, 그리고 Differential Net이 얼마만큼의 길이 차이를 보이는지 등에 대한 결과를 한눈에 확인할 수 있습니다.

그림5. Critical Differential Net Matching 설계 규칙 위반 검출

이렇게 설계 규칙을 위반한 Net가 발견되게 되면, 해당 Net를 위반 사항을 참고하여 설계 수정을 진행해 보실 수 있습니다. 해당 Differential Net의 경우 Net의 길이가 1.3723 [mm]만큼 차이가 나는 부분의 Layout을 수정하여 Net의 길이를 맞춰주는 과정을 진행하였습니다. 아래 그림의 왼쪽의 PCB에서 오른쪽의 PCB로 Net의 길이를 수정하였습니다.

그림6. 두 Differential Net 길이를 맞춰주는 과정 진행

수정을 진행한 후 해당 PCB에 대한 신호 무결성 해석을 진행해 보았습니다. 아래의 결과는 Net의 길이 수정을 진행하기 전과 후의 공통 모드 전류의 결과를 확인해 본 내용으로, 초록색의 수정을 진행하기 전의 공통 모드 전류의 경우 Noise 성분의 최대치가 높게 설정되는 반면 빨간색의 수정 이후의 공통 모드 전류 결과를 보면 Noise 성분의 최대치가 많이 감소된 결과를 확인해 볼 수 있었습니다.

그림7. PCB 설계 수정 전후 신호 무결성 결과 확인

결론

다쏘시스템의 전자기장 해석 솔루션인 CST Studio Suite에는 신호 무결성과 전원 무결성에 대한 분석을 2.5D로 빠르게 진행할 수 있는 CST PCB Studio를 제공하고 있으며, 그 안에는 포스팅을 통해 설명했던 PCB에 대한 설계 규칙 가이드 위반사항을 빠르게 검출할 수 있는 CST BOARDCHECK®을 제공하고 있습니다. 또한 3D 전자기장 해석을 진행할 수 있는 CST Microwave Studio를 통해서도 PCB를 3D로 불러오기 하여 고주파 대역에서 나타나는 전자기 Coupling을 고려한 보다 정확한 신호 무결성 및 전자파 적합성 분석이 가능합니다. CST에서 제공하는 다양한 해석 제품들을 이용하여 PCB에 대한 분석을 다방면으로 분석해 보시길 바랍니다.

본 자료는 다쏘시스템의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템

관리자

2023.05.31

조회 445

|

|

|

[문서] CST Studio Suite을 이용한 고속 Backplane simulation

본 게시물에서는 SIMULIA의 진정한 Transient EM/Circuit Co-Simulation을 사용하여 신뢰할 수 있는 Backplane을 설계하는 방법을 보여드리고자 합니다. 실제 프로토타입을 테스트하지 않고도 simulation에서 KPI 및 성능 지수(예: eye 다이어그램)를 계산하는 방법을 보여주고, Macro 모델 Circuit simulation 방법에 비해 Transient Co-simulation(tran-co)의 이점을 소개합니다.

IBIS-AMI를 사용한 Backplane 모델링 소개

긴 도달 거리의 Backplane 설계는 까다로운 작업입니다. 일반적으로 데이터 속도는 최대 수십 기가비트이고 채널 길이는 약 1미터입니다. loss tangent = 0.02인 FR4와 같은 기존 유전체는 이렇게 긴 채널에서 상당한 삽입 손실(IL)을 초래합니다. IL을 완화하려면 손실이 낮은 새로운 재료가 필요합니다. 송신기, 수신기 및 커넥터의 라인 임피던스는 낮은 반사 손실(RL)을 달성하기 위해 일치해야 합니다.

입출력 buffer 정보 사양(IBIS)[1]은 입출력(I/O) buffer 모델링을 위해 업계에서 널리 사용되고 있습니다. IBIS 알고리즘 모델링 인터페이스(IBIS-AMI)[1]를 사용하면 Serializer/Deserializer (SerDes) PHY의 필수 부분인 공급업체별 이퀄라이제이션 및 클록 복구 알고리즘을 사용할 수 있습니다. AMI simulation의 첫 번째 단계는 passive 채널 및 I/O buffer 모델의 임펄스 response을 구하는 것으로, 이는 Step response의 미분과 동일합니다.

진정한 Transient EM/Circuit Co-simulation

기존 workflow에서는 passive 채널의 산란 파라미터(S-parameter)를 먼저 계산한 다음 표준 macro 모델링을 통해 SPICE 모델로 변환합니다. 결국 SPICE 모델을 simulation하여 Step response을 얻습니다.

기존 Workflow와 비교하여 새로운 Transient EM/Circuit Co-simulation(tran-co) 방법[2]을 도입하여 S-parameter와 macro 모델을 사용하지 않고 Step response을 계산하며, 이는 시간 영역에서 맥스웰 방정식과 Circuit 요소(예: IBIS 모델 또는 AC 커플링 커패시터)를 함께 풀 수 있습니다. 기존 workflow보다 더 빠르며 비물리적 동작을 피할 수도 있습니다.

Backplane passive 채널의 삽입 손실

1미터 길이의 passive 채널을 설계하기 전에 더 짧은 테스트 보드 세 개를 테스트합니다.

A. 테스트 보드 A: 손실 탄젠트 = 0.02, 유전율 = 4.2, 불일치 임피던스의 유전체,

B. 테스트 보드 B: 손실 탄젠트 = 0.008, 유전율 = 3.2, 불일치 임피던스의 유전체,

C. 테스트 보드 C: 손실 탄젠트 = 0.008, 유전율 = 3.2, 송신기와 수신기에서 100Ω의 일치하는 Differential 임피던스를 가진 유전체.

그림 1. 금속 재료와 동일한 크기와 구리를 사용한 세 개의 테스트 보드 A, B, C

simulation 결과는 다음 그림에 요약되어 있습니다. 다음 왼쪽 그림에서 곡선 A와 B의 SDD21을 비교하면 유전체 손실이 삽입 손실에 미치는 영향을 관찰할 수 있습니다. 1m 길이 채널의 경우 손실 탄젠트 = 0.02인 FR4와 같은 일반적인 유전체는 상당한 삽입 손실을 초래하며, 150mm 채널의 경우 이미 -12dB로 떨어집니다. 따라서 손실이 낮은 신소재가 선호됩니다. 오른쪽 그림에서 B와 C의 SDD11 곡선을 비교하면 특히 differential pairs의 단면이 크게 변할 수 있는 비아와 커넥터에서 임피던스를 일치시키는 것이 중요하다는 것을 알 수 있습니다.

그림 2. 테스트 보드 A, B, C의 simulation 결과(왼쪽: SDD21, 오른쪽: SDD11)

SerDes Step response의 macro 모델

다음에서는 IBIS Tx/Rx buffer 모델, AC 커플링 커패시터 및 3D passive 채널이 포함된 SerDes 채널의 Step response을 계산합니다.

그림 3. 전체 simulation 네트워크에는 3D 모델과 Circuit 요소가 포함

3D passive 채널의 S-parameter를 먼저 계산한 다음 macro 모델로 변환하여 time domain에서 Circuit 요소(예: IBIS 모델 및 AC 커플링 커패시터)와 함께 simulation하여 Step response을 얻을 수 있습니다. 이 블로그에서는 이 workflow를 기존 또는 Circuit workflow라고 합니다. 그러나 긴 passive 채널(예: 최대 simulation 주파수 λ의 자유 공간 파장이 수십 λ인 경우)의 경우 S-parameter 계산에 많은 시간이 소요될 수 있으며 기존 macro 모델링 프로세스는 비효율성(최종 Circuit의 크기가 크기 때문에)과 시스템 레벨 simulation의 정확도 저하(전파 지연의 부정확한 모델링으로 인해)를 초래할 수 있습니다. 이러한 이유로 본 논문에서는 S-parameter나 macro 모델을 계산할 필요 없이 3D passive 채널과 Circuit 소자를 시간 영역에서 단계적으로 함께 풀어서 step response을 구하는 Tran-co Workflow[2]를 소개합니다. Circuit와 Tran-co Workflow를 테스트 보드 C에 적용하여 그 성능을 다음 표에 요약했습니다.

Table Ⅰ. Simulation statistics of Test board C

Max. Freq. Board Length Mesh Cells Circuit Tran-co

112 GHz 150 mm ≈ 56 λ 68,186,250, 117 min 86 min

위 표에서 볼 수 있듯이 Tran-co Workflow 해석 결과로 simulation은 CPU @2.0GHz, GPU 2xKepler Tesla K40c+m, 256GB RAM이 장착된 머신에서 실행되었습니다.

Transient co-simulation과 macro 모델 Circuit simulation 비교

Tran-co Workflow의 Step response을 Circuit solver[3]에서 residues-poles형태(Foster Pole-Residue [2])를 사용하여 합성한 macro모델을 simulation하여 얻은 결과와 비교합니다. 아래 그림과 같이 덩어리 소자로 합성된 macro모델을 사용하면 Step response의 시작 부분에서 비물리적 ripple이 나타납니다(빨간색, 3_112GHz). 그러나 Tran-co Workflow(녹색, 6_112GHz)와 Circuit Workflow의 poles/residues macro모델(파란색, 포스터)의 결과는 서로 일치하며 비물리적인 거동을 피할 수 있습니다.

그림 4. step response(a)과 t = 0 주변 확대 보기(b)의 비교

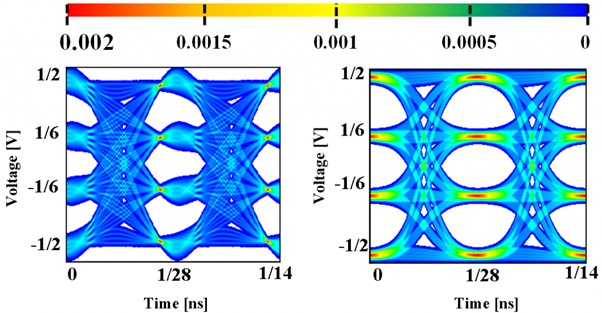

Circuit 및 Tran-co Workflow에 대한 통계적 Eye diagram이 생성됩니다. macro 모델이 덩어리 요소로 합성된 Circuit Workflow의 Eye diagram은 아래 왼쪽 그림과 같이 변형된 것을 확인할 수 있습니다. 아래 오른쪽 그림은 Tran-Co Simulation Workflow의 Eye diagram입니다.

그림 5. Circuit(a) 및 Tran-co(b) Workflow의 통계적 Eye diagram

Full 3D Backplane 채널 simulation

마지막으로 다음 그림과 같이 Tran-co Workflow를 따라 Backplane에서 1미터 길이의 채널을 simulation합니다. 전송 라인과 커넥터의 Differential 임피던스는 100옴으로 최적화되어 있습니다. 기판에는 유전율이 3.2인 무손실 유전체가 사용됩니다.

그림 6. Backplane의 완전한 3D passive 채널

Step response을 얻은 후 사전 탭 1개와 사후 탭 2개가 있는 3-taps-FFE(Feedforward Equalizer)와 3-taps-DFE (Decision Feedback Equalizer)를 사용하여 무작위 jitter를 포함하지 않는 통계적 Eye diagram을 개선합니다. 따라서 각 레벨의 확률 밀도(PD)에는 결정론적 jitter만 포함됩니다. Eye diagram의 결정적 jitter를 무작위 잡음으로 컨볼루션하여 아래와 같이 신호 대 잡음비(SNR)가 12dB인 PD를 얻습니다.

그림 7. Eye diagram의 점선으로 표시된 통계적 Eye diagram 및 전압 확률 밀도

Backplane simulation workflow 개요

SerDes simulation을 위한 SIMULIA CST 솔루션은 다음 그림에 요약되어 있습니다.

그림 8. SIMULIA CST SerDes 솔루션

GPU 가속 기능이 있는 CST Studio Suite® Time domain solver[2]는 SerDes 채널의 전기 대형 passive 인터커넥트를 효율적으로 simulation할 수 있습니다. IBIS-AMI [1] 및 HSPICE [3] simulation은 CST Design Studi에서 실행할 수 있습니다. version 2022에서는 컴포넌트 라이브러리에 IBIS-AMI 데모가 추가되어 사용자가 IBIS-AMI simulation을 원활하게 시작할 수 있습니다. CST Studio Suite® IDEM [2]은 S-parameter를 SPICE 모델로 변환하는 최첨단 macro 모델링 기법을 제공합니다. Eye diagram 툴을 사용하면 일반적인 SerDes 기술(예: 이퀄라이제이션 또는 4레벨 펄스 진폭 변조(PAM4))을 passive 채널 설계에 적용할 수도 있습니다. Eye diagram 툴은 사용자 정의 RJ(랜덤 jitter) 및 통계적 Eye diagram을 지원합니다. 마지막으로 simulation 결과(예: Differential S-parameter 또는 확률 밀도 함수)는 CST 및 Python의 VBA macro 편집기를 통해 쉽게 액세스할 수 있습니다. 따라서 사용자는 IBIS-AMI 표준[1]에서 지원하지 않는 Channel Operating Margin(COM)[4], Error Propagation(EP) 및 Forward Error Correction (FEC)과 같은 추가 분석을 VBA 및 Python 스크립트를 사용하여 수행할 수 있습니다.

References

1. IBIS Open Forum, https://ibis.org/.

2. Dassault Systèmes, https://www.3ds.com/simulia/

3. Synopsys Inc. https://www.synopsys.com/

4. IEEE Std. 802.3bj-2014.

저자 : Andreas Barchanski

Longfei Bai joined SIMULIA CST, Dassault Systèmes in 2015 as an application engineer supporting customers with EDA. He completed his B.S. from the University of Electronic Science and Technology of China in 2011 and M.S. degrees from Technische Universität Darmstadt in 2015 in the field of electrotechnics. His primary focus now is on SI, PI and EMC on PCB, package and chip.

본 자료는 다쏘시스템 코리아 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템코리아 블로그

관리자

2023.05.22

조회 464

|

|

|

[문서] Between Circuit and 3D Simulation: Broadband Macromodeling

본 게시글에서는 광대역 Macromodeling 및 Netlist/subcircuit 추출을 사용하여 S-파라미터로부터 SPICE 회로 시뮬레이션 모델을 생성하는 방법 및 전자 제품 설계를 위한 회로 및 3D field 시뮬레이션의 역할에 대해 설명합니다.

회로와 3D 시뮬레이션 사이의 광대역 Macromodeling

Dassault Systèmes, Michelangelo Bandinu

회로 시뮬레이션과 3D field 시뮬레이션 비교

전자 및 전기 공학에서 오랫동안 사용되어 온 시뮬레이션에는 크게 두 가지 유형이 있습니다. 회로 시뮬레이션은 회로 구성 요소의 전류와 전압을 모델링하며, 반도체와 같은 복잡한 비선형 구성 요소를 모델링할 수 있는 빠르고 강력한 기능을 제공합니다. 반면에 3D 전자기장 시뮬레이션은 공간을 통한 전자기장의 전파를 계산하고 원거리에 결합된 구성 요소 간의 상호 작용을 정확하게 포착합니다.

전통적으로 회로 시뮬레이션은 인쇄 회로 기판(PCB), 칩 패키지 및 집적 회로를 설계하는 데 사용되었고, 3D field 시뮬레이션은 안테나와 같은 무선 및 마이크로파 구성 요소에 사용되었습니다. 그러나 기존 PCB 및 칩패키지 내의 데이터 속도가 증가함에 따라 전자 신호의 주파수 또한 증가하여 이제는 사실상 마이크로파에 해당할 정도로 주파수가 증가하고 있습니다. 이는 신호가 신호 라인 내에서 격리된 상태로 유지되지 않고 PCB를 통해 전파되어 간섭 문제와 기타 신호 무결성(SI), 전력 무결성(PI), 전자파 적합성(EMC) 문제를 일으킬 수 있다는 것을 의미합니다.

시뮬레이션은 레이아웃 단계에서 이러한 문제를 분석하고 채널을 통한 데이터 전송을 모델링하여 문제를 식별할 수 있습니다. Eye diagram 및 bathtub과 같은 수치를 계산하고 잠재적인 완화 접근 방식을 테스트할 수 있습니다. 그러나 앞서 언급했듯이 고속 PCB의 전체 분석을 위해서는 회로 및 3D field 시뮬레이션의 측면이 모두 필요합니다.

Macromodeling이란?

다음은 광대역 Macromodeling이 필요한 이유입니다. 구성 요소의 Macromodeling은 3D field 시뮬레이션으로 계산된 S-parameter 데이터를 바탕으로 회로 시뮬레이션과 호환되는 방식으로 전자기 거동을 설명합니다. Macromodeling을 사용하면 복잡한 고속 전자장치의 SI/PI 및 EMC 시뮬레이션을 효율적으로 수행하여 잠재적인 문제를 식별하고 완화할 수 있습니다.

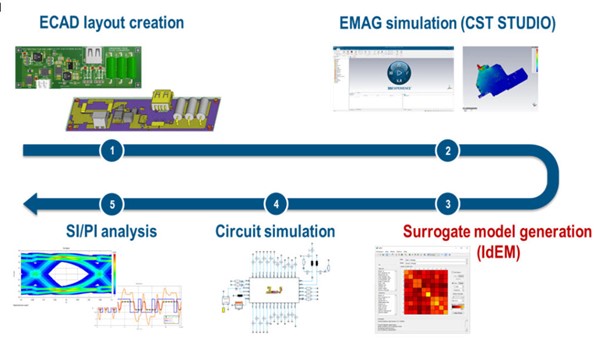

그림 1. Macromodeling과 PCB의 SI/PI 분석에 대한 Workflow

Macromodeling은 정확성을 유지하기 위해 두 가지 규칙을 준수해야 합니다:

첫째, Passive여야 합니다. 에너지 보존 법칙에 따르면 컴포넌트는 입력된 전력보다 더 많은 전력을 출력할 수 없습니다. 이를 위반하는 컴포넌트는 비현실적이며 시뮬레이션 문제를 일으킬 수 있습니다(전력이 증가하여 시스템이 수렴하지 않기 때문).

둘째, 인과관계가 있어야 합니다. 원인은 항상 시간적으로 효과보다 선행해야 하며, 상호 연결의 응답이 여기를 예상해서는 안 됩니다.

다쏘시스템 시뮬리아는 광대역 Macromodeling을 위한 솔루션으로 3D 전자기 시뮬레이션 툴인 CST 스튜디오 스위트와 Macromodeling링 모듈인 IdEM을 사용하여 충실도 높은 인과 관계의 수동 Macromodeling을 생성할 수 있습니다. IdEM은 모든 회로 시뮬레이션 툴과 함께 사용할 수 있는 SPICE(집적 회로 강조 시뮬레이션 프로그램) 모델을 생성합니다.

저자 : Michelangelo Bandinu

Michelangelo Bandinu received his Degree in Electronic Engineering from Politecnico di Torino, Italy in January 2005. In 2005, he worked as an Application Engineer at IBM Deutschland Entwicklung GmbH, Boeblingen (Germany) within the IBM Packaging Development group. From 2006 to 2010, He was at Politecnico di Torino where he carried out research projects on modeling and simulation of interconnect structures. In 2007, Michelangelo co-founded IdemWorks s.r.l. (acquired in 2016 by CST AG – now Dassault Systèmes) serving as Managing Director and Product Manager of the IdEM product until the full integration of the company into Dassault Systèmes in 2019. He currently holds the position of SIMULIA R&D EMAG Application Senior Manager and leads the R&D IdEM team.

본 자료는 다쏘시스템 코리아 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템코리아 블로그

관리자

2023.05.12

조회 414

|

|

|

[문서] Extracting (partial) Inductance, Capacitance and Resistance from Electromagnetic Simulation

루프 및 Partial 인덕턴스의 개념과 전자기 시뮬레이션에서 RLC 모델을 추출하는 방법에 대해 설명합니다.

CST Studio Suite의 새로운 RLC solver가 Partial RLC 모델의 시뮬레이션을 어떻게 개선하는지 살펴보고 본드 와이어가 있는 패키지 모델에 대한 RLC solver의 해석 모델도 살펴보도록 하겠습니다.

전자기 시뮬레이션에서 (partial) 인덕턴스, 커패시턴스 및 저항 추출

Dassault Systèmes, Andreas Barchanski

전자계 시뮬레이션에서 등가 모델을 추출하는 아이디어는 전자기장 시뮬레이션 자체만큼이나 오래되었습니다. 물리적 구조의 특성을 그 거동을 적절히 모사할 수 있는 등가모델로 변환할 경우 시스템 또는 회로(SPICE) 시뮬레이션과 같은 추가 처리에 이러한 모델을 사용할 수 있습니다. 이러한 등가모델을 모사하여 해석에 사용하는 대표적인 예로는 고전력 부품을 연결하는 버스 바, PCB의 신호 trace, 고속 채널의 긴 비아 또는 패키지의 본드 와이어 등이 있습니다. 모든 전기 엔지니어라면 저항, 인덕턴스, 커패시턴스(RLC)로 구성된 Lumped network로 변환된 등가회로를 매우 자연스럽게 사용가능합니다. 이러한 접근 방식은 구조 크기가 관심 주파수의 파장의10분의 1보다 작은 경우 잘 동작됩니다.

전자파 적합성(EMC) 및 전자 설계 자동화(EDA) 애플리케이션에서 구조의 인덕턴스는 kHz 범위 이상의 주파수에서 전체 임피던스의 지배 인자가 되므로 특히 중요합니다. 대partial의 전기 엔지니어는 인덕턴스라는 용어를 들으면 즉시 신호 링잉에 대해 생각할 것입니다. 따라서 오늘의 포스팅에서는 전자기장 시뮬레이션을 통한 인덕턴스 계산에 대해 좀 더 자세히 살펴보겠습니다.

전통적으로 인덕턴스는 라인 전류 𝐼로 둘러싸인 표면 S를 통과하는 자속으로 정의됩니다. 자속은 표면을 적분하여 B에서 계산할 수 있으므로 다음과 같이 구할 수 있습니다:

표면을 정의하려면 항상 폐쇄 루프가 필요하기 때문에 이를 루프 인덕턴스라고 합니다. Fullwave solver에서 폐쇄 루프 인덕턴스를 추정하는 것은 매우 간단합니다. 해석을 위해 S-parameter port에 의해 닫힌 전도성 루프를 정의합니다. 템플릿 기반 후처리를 사용하여 S-parameter를 Z-parameter로 변환하거나 직접 인덕턴스로 변환합니다. 동일한 단계를 통해 루프의 저항도 계산할 수 있습니다. 루프 인덕턴스는 전류가 항상 루프에서 흐르기 때문에 시스템의 물리적 동작과 밀접한 관련이 있습니다. 그러나 전자 설계자에게 반드시 가장 적절한 결과는 아닙니다.

최신 전자 시스템에서 전체 전류 루프는 여러 PCB, 케이블 및 커넥터를 통해 흐르는 기하학적으로 매우 복잡할 수 있습니다. 설계자는 종종 전류 루프의 특정 섹션이 전체 인덕턴스에 어떻게 기여하는지에 관심이 있습니다. 이것이 partial 인덕턴스 개념의 출발점입니다. 전류의 일부 구간(예: 위 그림에서 직사각형의 아래쪽 구간)에서만 기여도를 계산하려는 경우 더 이상 폐쇄 루프가 없으므로 위의 공식을 사용할 수 없습니다. B와 같은 전계량을 계산하는 대신 우회하여 𝑩 = 𝛻 × 𝑨로 자기장과 관련된 적절하게 선택된 벡터 전위 A를 계산해야 합니다. 본 포스팅을 통해 모두 소개하기 어려운 자기장 이론이 이를 설명하는데 포함되나 자세한 내용은 다루지 않겠습니다. 이 계산은 "표준" Fullwave solver로는 수행할 수 없으며 특수한 solver가 필요하다는 것입니다.

전통적으로 partial 인덕턴스 계산은 PEEC(partial mesh 등가 회로 방법)라는 수치적 방법으로 이어집니다. 이 방법은 모멘트 방법(MOM)과 밀접한 관련이 있으며 수년 동안 partial 수량 계산에 사용되어 왔습니다. 그러나 이 방법에는 복잡한 CAD 구조에 적용하기 어려운 특수 메시가 필요하다는 단점이 있습니다. 또한 자성 재료 특성과 관련된 몇 가지 문제가 있으며 mesh element의 수에 따라 스케일이 심하게 확장됩니다.

따라서 SIMULIA는 위에서 언급한 어려움을 겪지 않는 다른 접근 방식을 사용하여 partial 추출을 처음부터 다시 생각하기로 결정했습니다. CST Studio Suite의 RLC solver는 지난 몇 년 동안 많은 애플리케이션에서 효율적인 선택으로 입증된 유한 mesh법(FEM)을 기반으로 합니다. 이 solver는 복잡한 구조 형상을 처리할 수 있으며 곡선 메시 mesh도 사용할 수 있습니다. 매우 효율적으로 확장할 수 있어 복잡한 CAD 구조를 가져온 경우에도 바로 사용할 수 있습니다. 고투자율 및 고투과성 재료를 처리할 수 있으며 근사치 없이 DC에서 고주파까지 풀 수 있습니다. 추출된 RLC 값은 직접 판독할 수 있도록 CST Studio Suite 1D results에 plot되거나 SPICE 파일로 내보낼 수 있습니다. 단일 주파수 및 광대역 내보내기가 모두 가능합니다.

partial RLC 추출의 주요 적용 분야는 일반적으로 파장보다 훨씬 작은 구조입니다: 예를 들어, 관심 주파수가 MHz 범위인 전력 전자 애플리케이션의 버스바 또는 주파수는 수 GHz일 수 있지만 본드 와이어의 길이가 다소 짧은 패키지의 본드 와이어등의 해석이 이에 해당합니다. 사람이 판독할 수 있는 RLC 값을 추출하는 것은 RLC 접근법의 매우 중요한 장점이며 구조의 동작을 이해하는 데 도움이 됩니다. 이 방법은 mesh 수가 많은 시스템을 판독하고 해석하는 것이 점점 더 어려워지기 때문에 구성 mesh 수가 적은 모델에 가장 효과적입니다. 블랙박스 유형의 모델이 필요한 시스템 레벨 시뮬레이션의 경우 일반적으로 Fullwave solver와 S parameter를 사용하는 것이 좋습니다. 필요한 경우 벡터 피팅을 사용하여 S parameter를 SPICE 모델로 변환할 수 있습니다.

아래 예제에서는 팬 아웃 trace가 있는 패키지 본드 와이어의 인덕턴스 추출을 살펴보겠습니다. 이 패키지는 최첨단 패키지 설계 소프트웨어를 사용하여 설계되었습니다. 이 설계는 사용자가 가져올 패키지의 네트와 섹션을 추가로 선택할 수 있는 강력한 built-in import인터페이스를 사용하여 CST Studio Suite로 직접 가져왔습니다. 보다 명확한 이해를 위해 모델에 색을 입혔습니다: 관심 네트 B_DQ_14는 파란색, VCC는 빨간색, GND는 녹색입니다. 기판은 시뮬레이션에 포함되지만 아래 그림에서는 숨겨져 있습니다.

partial 인덕턴스의 경우 A 지점에서 B 지점까지의 경로를 패키지 연결의 인덕턴스로 정의하는 것은 매우 간단합니다. 그러나 루프 인덕턴스의 경우 칩 내부의 실제 라우팅에 따라 전류 루프가 닫힐 가능성이 여러 가지 있습니다. 실제 칩에서 패키지의 속성을 분리하려는 경우 partial 추출을 통해서만 가능합니다. 그래도 결과를 살펴보고 partial 인덕턴스, partial 접근법을 사용하여 계산된 루프 인덕턴스 및 전파 솔버를 사용하여 계산된 루프 인덕턴스를 비교하는 것은 가치가 있습니다. 데모 목적으로 본드 와이어 C와 D를 선택했습니다. 루프를 닫기 위해 B에서 C로, B에서 D로 각각 금속 연결을 추가합니다.

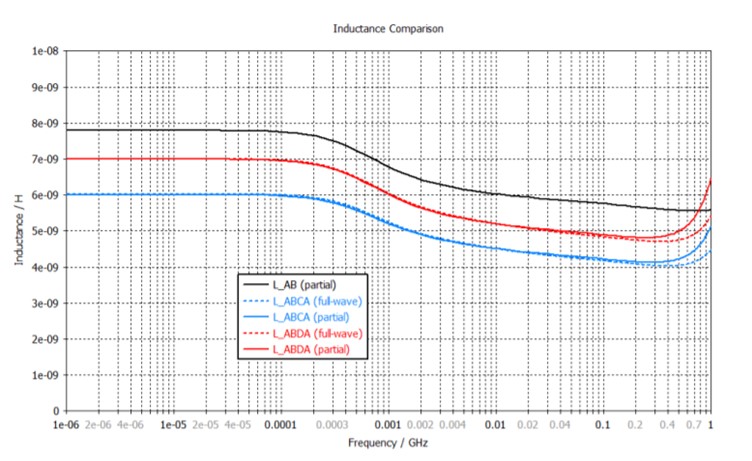

인텔 i7-7820HQ 프로세서가 장착된 노트북에서 partial RLC 솔버의 경우 약 7분, 전파 솔버의 경우 약 15분 정도 시뮬레이션이 소요됩니다. 다양한 경우의 인덕턴스는 위 그림에 표시되어 있습니다. 일반적인 동작을 관찰할 수 있습니다: 100kHz 이하에서는 인덕턴스 값이 가장 높으며, 이 영역을 종종 DC 인덕턴스라고 합니다. 1MHz 주변에서는 skin effect 효과로 인해 감소하고 100MHz 주변에서는 소위 AC 인덕턴스가 있습니다. 대partial의 경우 이 두 영역은 예제에서보다 훨씬 더 평평합니다. 이 예에서는 패키지 모델의 도체 치수가 작기 때문에 DC에서 AC로의 전환 범위가 매우 넓습니다. 1GHz 부근에서 값의 증가를 관찰할 수 있습니다. 이 주파수는 파장 대비 루프의 전기적 길이가 약 𝜆/10이 되는 주파수이며, 더 이상 단일 인덕턴스 값을 사용하여 루프의 전기적 특성을 정확하게 설명할 수 없습니다. partial 인덕턴스 AB는 루프 인덕턴스 ABCA 및 ABDA보다 높습니다. 이는 전체 루프가 포함될 때 리턴 전류가 결과 인덕턴스를 감소시키기 때문에 일반적인 결과입니다.

저항을 계산할 때는 인덕턴스와 정확히 동일한 접근 방식을 사용할 수 있습니다. 그러나 커패시턴스의 경우 정전기 시뮬레이션과 매우 유사한 다른 단계를 해결해야 합니다. partial 커패시턴스의 개념은 물리적인 해석이 부족하기 때문에 혼란스러울 수 있습니다. 커패시턴스는 전도체의 속성이므로 두 개의 전도체는 하나의 커패시턴스 값(자체 커패시턴스 생략)으로 설명할 수 있습니다. 그러나 partial 인덕턴스 계산에 필요한 것처럼 하나의 도체에 여러 노드가 정의되어 있는 경우, 예를 들어 SPICE 내보내기와 같은 일관된 모델을 생성하려면 전도체의 커패시턴스를 이러한 노드에 분산시켜야 합니다. 이것이 partial 커패시턴스 개념의 배경이 되는 아이디어입니다.

이 블로그 게시물에서는 전자기 시뮬레이션을 통해 RLC 값을 추출하는 몇 가지 주요 아이디어를 설명하려고 노력했습니다. 기억해야 할 핵심 사항은 다음과 같습니다:

단일 RLC 값은 전기적으로 작은 구조의 특성을 설명하는 데 사용할 수 있습니다.

루프 인덕턴스는 물리적으로 중요하지만, partial 인덕턴스를 추출하면 구조의 분리된 섹션의 기여도를 추정할 수 있으므로 전자 제품 설계자에게 매우 유용할 수 있습니다.

frequency dependent 인덕턴스는 일반적으로 DC 및 AC 인덕턴스라고 하는 두 개의 영역을 나타냅니다.

partial 커패시턴스 개념은 하나의 전도체에서 여러 노드에 커패시턴스를 분배하는 데 사용됩니다.

저자 : Andreas Barchanski

Andreas is a senior solution consultant for electromagnetic simulation at Dassault Systèmes in Darmstadt, Germany. After receiving his PhD in numerical electromagnetics from the Darmstadt University of Technology in 2007 he joined CST which later became a part of Dassault Systèmes. His main interest lies in the simulation of electromagnetic compatibility of electronic systems, ranging from high-speed to power electronics.

본 자료는 다쏘시스템 코리아 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템코리아 블로그

관리자

2023.04.25

조회 480

|

|

|

[문서] Thermal Simulation of Electric Losses on PCBs, Compared to Measurements

다쏘시스템사의 CST Studio Suite을 이용한 발열 해석에 대한 내용을 살펴보겠습니다.

본자료에서는 IR-Drop 분석을 사용하여 CST Studio Suite에서 PCB 열 시뮬레이션을 위한 빠르고 효율적인 Workflow를 보여주고 이러한 접근방식의 효율성을 소개합니다.

측정과 비교한 PCB의 전자기 손실에 의한 발열 시뮬레이션

Dassault Systèmes, Marcel Plonka

Thermal simulation은 실제 프로토타입을 제작하기 전에 PCB의 온도 분포를 밝힐 수 있습니다. 이 문서는 IR-Drop 분석을 사용하여 CST Studio Suite에서 PCB Thermal simulation을 위한 빠르고

효율적인 워크플로우를 보여주고 이 접근 방식의 이점을 보여줍니다. 시뮬레이션 결과는 또한 측정에 대해 검증됩니다. 이 분석에서는 인클로저가 없는 PCB를 고려합니다.

모델 준비 단계를 가능한 한 단순하게 유지하기 위해 Thermal simulation에 참여하는 데 필요한 모든 필수 데이터는 IR-Drop 분석(예: 열원, PCB의 열 손실, PCB Components의 형상)에서 얻습니다.

Thermal simulation은 작업에 가장 적합한 CST Studio Suite conjugate heat transfer solver(CHT)로 실행됩니다. 이 접근 방식을 사용하면 작업 흐름에서 사용자가 PCB에 납땜된

Components 각각에 대해 등가 열 모델(예: 2 Resistor)을 수동으로 검색하고 정의할 필요가 없기 때문에 모델 설정 중에 많은 시간을 절약할 수 있습니다.

또한 CHT 분석을 사용하면 사용자가 모델에서 Thermal Surface properties을 설정할 필요가 없습니다. 필요한 경우 3D co-simulation을 통해 AC 손실을 시뮬레이션에 추가할 수도 있습니다.

Simulation 셋업 및 IR-Drop

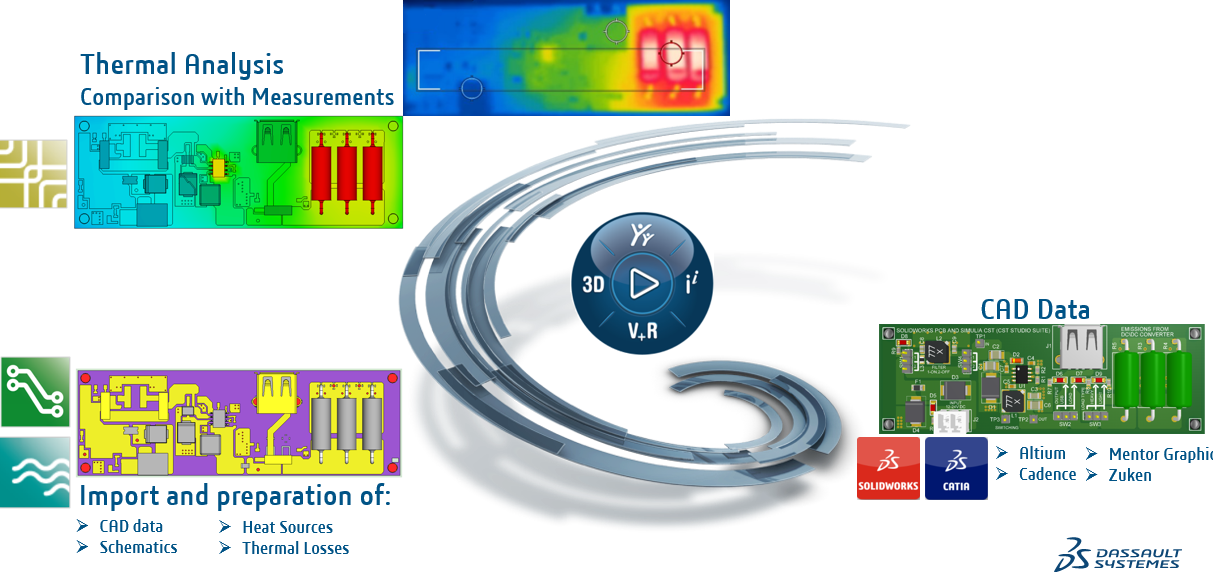

그림 1에서 볼 수 있듯이 시뮬레이션 프로세스는 비교적 간단합니다.

첫째, 사용자는 필요한 모든 데이터(예: E-, M-CAD 모델, 스택업 및 회로도가 포함된 PCB 레이아웃, PCB component 모양 등)를 수집합니다. 오늘날에는 거의 모든 정보가 이미 잘 알려진 EDA 툴로

생성된 파일에 저장되어 있습니다.

둘째, 사용자는 EDA 레이아웃을 CST Studio Suite로 가져와서 무결성을 검증하고 회로도를 기반으로 IR-Drop 분석을 설정하고 실행합니다.

그림 1. Workflow에 대한 빠른 개요

그림 2. CAD 데이터 가져오기 단계의 개요

IR-Drop 분석은 사용자가 Thermal 모델의 복잡성 수준을 결정할 수 있도록 많은 정보를 제공합니다. 예를 들어, PCB 레이어 내에서 계산된 전력 손실이 부품 손실에 비해 상대적으로

낮다는 것을 알 수 있습니다(그림 3 참조).

따라서 CST Studio Suite의 스택업 단순화 메커니즘을 활성화하여 동일한 열 특성을 가지면서도 훨씬 덜 복잡하고 시뮬레이션 시간을 단축할 수 있는 모델을 생성하고 사용할 수 있습니다.

그림 3. IR-Drop 결과를 기반으로 한 Thermal 모델 단순화의 가능성

그림 4. 5W 부하로 분석된 Thermal 모델

Thermal Simulation

Thermal simulation은 두 가지 전기 부하 조건에 대해 수행됩니다: 1.5와트 및 5와트(W).

부하 1.5W에 대해 지정된 모델은 그림 3에, 5W에 대해 지정된 모델은 그림 4에 나와 있습니다.

입력된 CAD 데이터를 기반으로 사용자는 PCB Components의 복잡성이 다른 여러 케이스를 설정하고 분석할 수 있습니다(그림 3 참조).

그림 3, 4와 같이 해석을 위해 사용된 모델의 구조는 PCB import를 통해 자동으로 생성된 단순화 모델을 A, B, C로 형상합니다. 이때 모델 A의 경우 power resistor들을 3D CAD import 기능을 통해

가져와 설정하며, Model C는 모델 B의 power resistor 모델을 생략한 모델입니다. Components는 워크플로에 의해 자동으로 할당되는 기본 재료로 열전도율(열전도도)이 5W/K/m인 것이 특징입니다.

전력 resistor와 커넥터(J1,, J2)는 예외입니다. 이러한 Components의 열전도도는 공개적으로 이용 가능한 정보를 기반으로 실험적으로 선택됩니다.

파워 resistor의 코어는 일반적으로 유리 섬유 또는 세라믹 재질로 구성되며, 이는 < 0.5 - 3 > W/K/m 범위의 열전도도로 설정됩니다. resistor 리드는 열전도도가 401W/K/m인 구리로 정의됩니다.

커넥터 J2는 열전도도가 1.5W/K/m인 유전체 재료로 만들어졌습니다.

USB 커넥터(J1)의 시뮬레이션 모델은 단순화되었습니다. 쉘은 237W/K/m의 열전도도를 가진 알루미늄으로 모델링 되었으며 "내부"는 1.5W/K/m의 열전도도를 가진 재료로 추정되며,

PCB Components에는 Thermal 패드가 포함되어 있지 않으므로 모든 Components에는 PCB 스택업에 대한 contact property이 할당됩니다.

실험적으로 측정된 에어 갭의 두께는 < 50 - 200 > μm의 범위에서 다양합니다. 시뮬레이션에는 50μm가 사용되었습니다.

참고 1: 모델 A, B는 PCB 오른쪽에 위치한 3개의 전력 resistor(스루홀 타입)는 1.5W를 방출합니다(온도는 resistor R3에서 측정).

참고 2: 모델 C는 USB 포트(J1)를 통해 연결된 외부 resistor에서 5W 방출을 분석했습니다. on-Board resistor은 PCB에서 전기적으로 분리되어 있습니다.

측정 설정

측정은 열화상 카메라(열화상 카메라)와 두 개의 프로브(K-타입 열전대 프로브 및 실내 온도계)의 도움을 받아 판독 값을 검증합니다.

프로브는 열화상 목적으로 테스트된 디바이스 방사율과 주변 온도의 정확한 값을 얻는 것입니다. 획득한 온도 값을 기반으로 모든 측정 지점에 대한 평균 온도가 계산됩니다.

프로브 위치는 그림 5에 나와 있습니다.

참고 3: 수행된 테스트는 인증된 측정 유형으로 분류되지 않습니다.

그림 5. 부하 조건에 대한 측정 세부 사항: 1.5W.

측정 오차와 단순화된 Thermal 모델 시뮬레이션을 기반으로 시뮬레이션과 측정 결과 간의 최대 편차를 +/- 4°C 수준으로 추정합니다.

모든 비교 온도는 다음 표에 나열되어 있습니다(그림 6 및 그림 7). 시뮬레이션 온도가 한계를 초과하는 경우 표의 해당 필드는 주황색으로 표시됩니다.

(a) 1.5W 부하에 의한 모델의 온도 비교.

(b) 5W부하에 의한 모델의 온도 비교.

그림 6. 부하에 따른 발열 해석 및 측정 결과

모델 A와 B의 시뮬레이션은 사용자 요구에 따라 CAD 형상의 복잡성 수준을 고려해야 함을 나타냅니다.

그림 6a에서 볼 수 있듯이 모델 B는 모델 A보다 거의 4배 더 빠르게 실행되지만 두 모델 간의 전반적인 온도 편차는 크지 않습니다.

단순화된 CAD 형상을 사용하면 사용자가 더 많은 시뮬레이션 실험을 수행하고 다양한 시나리오에서 디바이스 동작에 대해 더 많은 것을 배울 수 있으며, 이는 특히 설계 단계에서 항상 유용합니다.

그림 6(6a, 6b)은 디바이스 로딩 조건에 따라 시뮬레이션의 정확도 및 해석의 효율성이 달라질 수 있습니다. 따라서 이부분은 위 사항을 고려하여 사용자가 적절한 수준을 선택하시면 됩니다.

Thermal solver에 필요한 입력 parameter(데이터)를 계산하기 위해 CST Studio Suite 워크플로우에서 IR-Drop 분석을 수행한다는 점을 기억하는 것이 중요합니다. IR-Drop 분석은 회로의 계산된

전압 및 전류를 기반으로 DC 레벨에서만 PCB의 전력 손실을 얻습니다. 따라서 AC 전력 손실은 고려되지 않습니다. 이를 고려하기 위해 CST Studio Suite에서 3D co-simulation을 수행할 수 있습니다.

그림 7. DC 및 AC 손실을 포함한 열 시뮬레이션 결과 비교.

분석된 장치는 SMPS(스위치 모드 전원 공급 장치) 제품이며, 이는 장치가 출력 전압/전류 레벨을 제어하는 데 사용하는 스위칭 메커니즘으로 인해 전력 전송의 일부가 스위치에서 생성된 고주파를

통해 발생한다는 것을 의미합니다. 이 부분의 크기는 스위칭 토폴로지뿐만 아니라 부하 조건에 따라 달라집니다.

다행히도 CST Studio Suite에서는 사용자가 이전에 가져온 PCB의 3D 모델을 매우 빠르게 생성하고 집적 회로 시뮬레이터와 함께 레이아웃 및 온보드 Components의 추가 AC 손실을 계산하는

소위 3D co-simulation을 실행할 수 있습니다. 이 접근 방식은 AC 손실이 지배적인 모든 PCB Components에 유용합니다. 예를 들어, 코어 손실, 권선의 AC 및 DC 저항 손실로 인해 전력 손실이

발생하는 전력 인덕터, 변압기, 초크 및 기타 관련 Components; 전도, 스위칭 메커니즘 및 게이트 전하 손실로 인해 손실이 발생하는 스위치(IGBT, MOSFET 트랜지스터)등이 대표적입니다.

분석된 PCB에 co-simulation을 적용하면 그림 7과 같은 결과를 얻을 수 있으며, 측정 결과와 시뮬레이션 결과 간의 일치에 도달할 수 있습니다. 시스템 인덕터(L1)의 온도가 최대 허용 오차를

약간 초과하는데, 이는 주로 코어에 사용된 소재가 알려지지 않았기 때문입니다. IR-Drop 솔버를 사용한 PCB의 Thermal simulation은 설정 및 실행이 비교적 빠릅니다.

모든 시뮬레이션 사례는 4코어 인텔® i7-6820hq® 프로세서가 장착된 노트북에서 실행되었습니다. 계산된 결과의 정확도는 분석된 시스템에 존재하는 손실의 특성에 따라 달라집니다.

AC 손실이 지배적인 경우, 이를 정확하게 캡처하고 열 분석에 추가하기 위해 3D co-simulation을 실행하는 것이 좋습니다.

Summary

측정과 시뮬레이션 간의 일치하는 결과는 IR-Drop 및 CFD 워크플로우가 PCB의 electric loss로 인한 발열을 계산하는데 효과적인 방법임을 보여줍니다.

이 블로그 게시물에서 시연된 워크플로우는 표준 EDA 레이아웃 파일에서 쉽게 설정할 수 있으며 단일 노트북과 같은 로컬 리소스에서 실행할 수 있습니다.

CST Studio Suite는 전자 엔지니어가 물리적 테스트 보드 없이도 설계의 열 성능을 빠르게 평가하는 데 사용할 수 있는 강력한 툴을 제공합니다.

본 자료는 다쏘시스템 코리아 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템코리아 블로그

관리자

2021.10.25

조회 1183

|

|

|

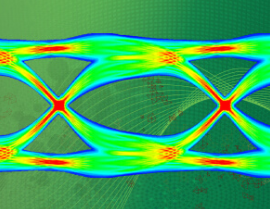

[문서] Jitter Compliance of SerDes Channels

SerDes 채널에 대한 데이터 속도가 계속 증가함에 따라, 신호 무결성(SI : Signal Integrity)은 설계 프로세스에서 점점 더 중요해지고 있습니다. 패시브 채널에서 좋은 S-Parameter(예: 낮은 삽입 손실)가졌다고 해서 신호가 좋은 타이밍을 갖는지 또는 지터 컴플라이언스 테스트를 통과하는지 확인할 수 없습니다. jitter budget은 대개 낮은 비트 오류율로 정의되며, 시뮬레이션과 측정 모두 이 낮은 비트 전송률에서 jitter를 얻기가 어렵습니다. CST Studio Suite은 매우 사용하기 위훈 GUI환경 내에서 타이밍 분석(예: 데이터 독립 지터의 동일화, 인코딩 및 계산)을 위한 Eye-diagram 후처리 기능을 제공하고 있기 때문에 엔지니어가 효율적으로 지터를 분석할 수 있게 해줍니다. 사용되는 통계적 방법은 매우 낮은 비트 오류율의 지터를 빠르고 정확하게 추정할 수 있습니다.

본 E-seminar에서는 다음과 같은 항목을 확인 가능합니다

1. 시뮬레이션 및 측정에 사용되는 지터 계산 방법론. 2. 복잡한 SerDes 채널을 3D로 시뮬레이션하고 UBS 3.1 Type C 커넥터의 예와 함께 Eye Diagram 도구를 사용하여 지터 분석을 수행하는 방법.

■ 자세한 내용 및 해석 사례는 다쏘시스템즈 홈페이지에서 확인 가능합니다.

https://events.3ds.com/jitter-compliance-of-serdes-channels#_ga=2.118066063.708294723.1601012363-863a9eb0-f6df-11ea-a6f6-4324f0f93f0b

관리자

2021.10.22

조회 932

|

|

|

[문서] Removable EBG-Based Common Mode Filter

전자기 밴드 갭 구조 (EBG라고 함)는 자연에서 발생하지 않는 전자기 특성을 갖도록 신중하게 설계된 구조 인 metamaterial 의 한 유형으로, 일부 주파수는 통과하고 다른 주파수는 차단하도록 조정할 수 있습니다. EBG를 표면 실장 구성 요소로 패키징하면 신호 간섭을 줄이는 데 사용할 수있는 common mode filter로 만들 수 있습니다. EBG는 기존 필터보다 훨씬 작으며 고밀도 상호 연결에서 소형화를위한 가능성을 제공합니다.

본 Whitepaper에서는 다음과 같은 항목을 확인 가능합니다.

1. CST Studio Suite®를 사용한 시뮬레이션을 사용하여 제거 가능한 EBG 필터를 설계하는 방법

2. 필터링 성능을 분석 및 최적화하고 신호 무결성 (SI)을 분석하기 위해 시간 영역 반사 측정법을 복제하기 위해 시간 및 주파수 영역 모두에서 필터를 모델링

3. 결과적으로 생성되는 R-EBG 구성 요소의 탁월한 간섭 필터링

■ 자세한 내용 및 해석 사례는 다쏘시스템즈 홈페이지에서 확인 가능합니다.

https://discover.3ds.com/removable-ebg-based-common-mode-filter#_ga=2.95559257.495784347.1601006821-863a9eb0-f6df-11ea-a6f6-4324f0f93f0b

관리자

2021.10.22

조회 962

|

|

|

[문서] eASIC (Customer Story)

Quick, Customizable Semiconductor Device Designs

eASIC은 Single Mask Adaptable ASIC ™ (application-specific integrated circuits) 전문 fabless 반도체 회사입니다. 고객의 특정 요구 사항을 염두에 두고 설계된 광범위한 Application에 대한 맞춤형 Integrated Circuits을 생산합니다. 특히 신제품 개발 단계에서 고객을 효과적으로 지원하려면 빠르고 비용 효율적인 설계 및 제조 프로세스가 필요합니다.고속 Application 전용 Chip 설계 시, 중요한 것은 IC 자체의 동작 만이 아닙니다. Package 및 인쇄 회로 기판 (PCB)을 포함한 전체 채널이 성능에 영향을 미칩니다. eASIC는 설계 단계에서 PCB Layout을 고려함으로써 장치의 성능을 개선하고 설치 후 발생하는 문제의 위험을 줄일 수 있습니다.

Simulating the Complex Package-PCB Interface

전자기 시뮬레이션을 통해 엔지니어는 제조에 착수하기 전, 설계의 특성을 확인할 수 있습니다. PCB는 크고 복잡하지만 Package는 작고 복잡하기 때문에 한 번에 전체 시스템을 모델링하는 것은 계산 집약적이며 긴 시뮬레이션 시간과 많은 메모리 소비가 필요합니다. 이러한 이유로 eASIC은 시뮬레이션을 분할해 Package와 PCB를 별도로 모델링하기로 했습니다.이를 위해 eASIC은 Full-wave 3D 시뮬레이션 Tool인 CST Studio Suite를 선택했습니다. CST Studio Suite에는 시뮬레이션을 연계하고 cascade 할 수 있는 SAM (System Assembly and Modeling)이 포함 되어있어 시스템을 부품의 합으로 간주할 수 있습니다. 기존의 결합된 Package / PCB 모델은 두 부품을 분리하기 위해 나누었고 Interface에 reference plane이 있는 포트를 사용하여 연결되었습니다.

CST Studio Suite의 세분화 접근 방식을 통한 Package-PCB 공동 설계는 합리적인 시간에 비용 효율적인 서버 시스템에 장착된 모델과의 상호 연결에 대한 정확한 분석에서 3D EM 시뮬레이션 강도를 활용할 수 있도록 했습니다. 이것은 복잡한 디자인에서 Full 3D 시뮬레이션을 현실로 만드는 놀라운 방법입니다!”

- LianKheng Teoh / Manager for Package Design, eASIC -

Accurate Full-Wave Simulations in Half the Time

전체 모델의 시뮬레이션에 비해 SAM을 사용한 co-simulation은 훨씬 더 빠르고 계산 부담도 적었습니다. Co-simulation 결과는 Full-simulation 결과 및 실제 측정과 거의 일치했습니다. 또한 Time-Domain Reflectometry(TDR)과 같이 널리 사용되는 실험실 측정을 정확하게 모사할 수 있었습니다.CST Studio Suite를 사용하고 모델을 분할함으로써 eASIC은 전체 모델을 사용하는 시뮬레이션과 비교할 때 Multi-level PCB 및 Package 시뮬레이션에서 최대 5배의 속도 향상을 달성할 수 있었습니다. 이는 eASIC에 상당한 속도 이점을 제공하고 설계 프로세스를 단축하는데 도움이 되었습니다.

■ 원문은 다쏘시스템즈 홈페이지에서 확인 가능합니다.

https://www.3ds.com/insights/customer-stories/easic

관리자

2021.09.27

조회 1219

|