|

|

[문서] 항공기 낙뢰, EMP 시뮬레이션

항공기 낙뢰, EMP 시뮬레이션 설정(Using CST Studio Suite)

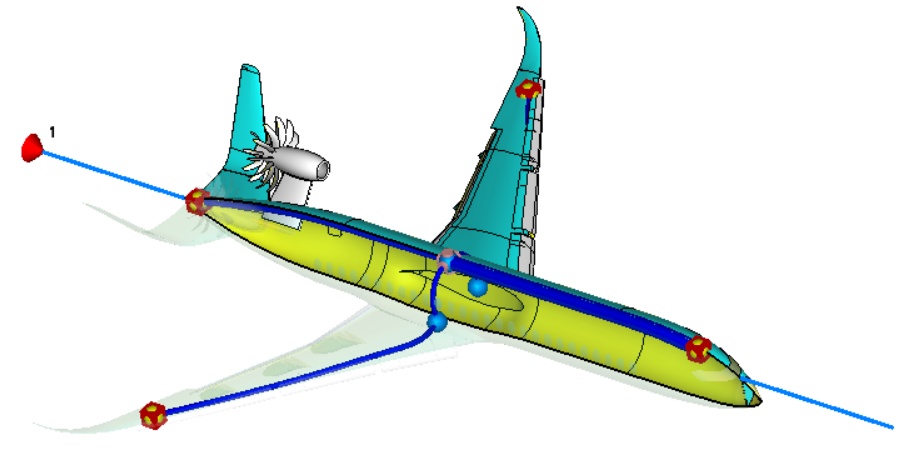

그림 1은 Cable 하네스를 포함한 항공기의 3D LEMP(낙뢰, EMP) 시뮬레이션 모델을 보여줍니다. Cable 하네스는 파란색 Cable 경로와 파란색 및 노란색 노드로 표시됩니다. 노란색 노드는 Cable 전류가 LEMP 시뮬레이션 모델의 3D 오브젝트로 흐르도록 합니다. 노란색 노드에 있는 빨간색 큐빅 프레임은 2023 버전부터 CST Studio Suite에서 사용할 수 있는 Cable 포트를 표시합니다. 항공기 외부의 파란색 전선은 포트 1(빨간색 원뿔로 표시됨)에 낙뢰 전류 파형을 주입할 수 있습니다. TLM solver의 경우 시뮬레이션 도메인의 Open boundary(여기에는 표시되지 않음)가 리턴 컨덕터 역할을 합니다.

그림 1. Cable 하네스를 포함한 항공기의 3D LEMP 시뮬레이션 모델

그림 2는 LEMP 시뮬레이션 모델의 Cable pin load(저항 및 단락) 및 probe(P1 - P8)를 포함한 Schematic 설정을 보여줍니다. pin 1에는 Transient Task의 여기로 정의되는 낙뢰 전류 파형이 주입되는 외부 포트 1이 부착되어 있습니다. probe를 사용하면 Transient pin 전압과 전류를 각각 모니터링하여 실제 Transient 레벨(ATL)을, 마지막으로 마진[1]을 추가하여 Transient Control Levels (TCL)을 산출할 수 있습니다.

그림 2. LEMP 시뮬레이션의 개략적인 모델

낙뢰 간접 효과 분석을 수행하기 위한 두 가지 워크플로우를 CST Studio Suite에서 사용할 수 있습니다. 아래에서는 CST Transient co-simulation 워크플로우와 CST traisnet task와 결과 결합 워크플로우에 대해 설명합니다. 첫 번째는 수년 전부터 사용 가능했지만, 두 번째는 Cable 포트가 3D로 도입된 CST Studio Suite 2023에서 사용할 수 있게 되었습니다. 이제 이 추가 기능을 통해 3D-EM-Cable Co-simulation을 3D로 실행하고 Schematic의 후처리 단계로 낙뢰 간접 해석을 수행할 수 있습니다.

CST Transient co-simulation workflow

CST Studio Suite의 낙뢰 간접 효과 분석을 위한 잘 정립된 워크플로우는 CST Transient co-simulation을 활용합니다. 일반적으로 3D 전자기(EM)와 다중 반도체 전송선(MCTL) 시뮬레이션을 양방향으로 결합합니다. 그림 3의 Schematic 보기의 Transient Task는 회로에 Cable pin load가 할당된 후 결합된 시뮬레이션을 제어합니다. 이 워크플로우의 단점은 Cable pin load와 다른 낙뢰 전류 파형이 변경된다는 점입니다. Cable pin load 또는 파형이 변경되면 Transient Task를 업데이트해야 하며, 이에 따라 3D-EM-Cable Co-simulation에 많은 시간이 소요됩니다.

그림 3. CST Transient co-simulation.

CST transient task with combine results workflow

결과 결합 워크플로우를 사용한 CST traisnet task는 Cable 하네스가 설치된 항공기의 3D 모델을 먼저 3D에서 Scattering parameters 측면에서 특성화할 수 있습니다. 그런 다음 실제 낙뢰 간접 효과 분석은 Schematic의 결합 결과를 사용하는 Transient Task를 통해 수행됩니다. 이는 Scattering parameters가 이미 3D로 계산되었기 때문에 순수한 후처리 단계입니다. CST Transient co-simulation의 경우처럼 전체 3D-EM-Cable Co-simulation을 반복하지 않고도 다양한 Cable pin load 구성과 낙뢰 전류 파형을 쉽게 조사할 수 있습니다.

워크플로 단계

1단계: 그림 4에서 워크플로는 Cable 하네스가 설치된 항공기의 3D full Wave 시뮬레이션으로 시작합니다. TLM solver는 Scattering parameters 측면에서 문제를 특성화하는데 사용됩니다. 항공기 스킨의 확산을 제대로 포착하려면 3D Transient simulation을 충분히 오래 실행해야 합니다. 필요한 시간은 고정된 값이 아니므로 사용자가 평가해야 합니다. 그림 4에 표시된 항공기 시뮬레이션의 경우 각 solver가 실행되는 데 40초면 충분합니다. 이 모델에는 11개의 포트가 포함되어 있으므로 11번의 solver 실행이 필요합니다.

그림 4. 3D-EM Cable 결합 3D 시뮬레이션.

2단계: 실제 낙뢰 간접 효과 분석은 Schematic의 후처리 단계로 수행됩니다. 이전 3D 시뮬레이션의 주파수 의존적 multi-port scattering parameters를 Transient lightning simulation에 정확하게 포함하기 위해 벡터 피팅이 사용됩니다. 그림 5에서 볼 수 있듯이 사용자는 built in 방식과 IDEM 방식 중에서 선택할 수 있습니다. 대부분의 경우 built in 방식이 이미 좋은 선택입니다. built in 방법으로 만족스러운 결과를 얻지 못하는 경우에는 IDEM을 선택할 수 있습니다. 종종 IDEM은 내장된 벡터 피팅보다 더 낮은 차수와 동일하거나 더 높은 정확도의 매크로 모델을 생성합니다.

그림 5. 벡터 피팅 방법 선택

3단계: 앞서 언급했듯이 그림 6에 각각 다른 Cable pin load 구성과 낙뢰 전류 파형에 대해 3D-EM-Cable Co-simulation을 반복할 필요가 없습니다. Schematic에서 회로의 일시적인 작업만 업데이트하면 됩니다. 3D-EM-Cable Co-simulation의 업데이트는 Cable 하네스가 설치된 항공기 모델이 수정된 경우에만 필요합니다.

그림 6. 여러 표준화된 전류 파형을 사용한 LEMP 분석

결론

앞서 설명한 두 워크플로 모두 장점이 있습니다. Cable pin 수가 많은 항공기 모델을 분석해야 하지만 LEMP 시뮬레이션을 하나 또는 몇 개만 수행해야 하는 경우에는 CST Transient co-simulation 워크플로우가 선호될 수 있습니다.

사용자가 다양한 Cable pin load 구성과 다양한 파형을 분석하는 데 관심이 있는 경우, 특히 3D-EM-Cable Co-simulation을 각 케이스마다 반복할 필요가 없기 때문에 결과 결합 워크플로우가 포함된 CST traisnet task 워크플로우가 선호될 수 있습니다. 또한 긴 펄스 지속 시간(예: 500us 이상)은 CST Transient co-simulation을 위해 며칠이 아닌 몇 초 만에 해결할 수 있습니다.

이제 사용자는 LEMP 시뮬레이션을 위한 두 가지 워크플로우를 사용할 수 있으며, 조사 중인 사례에 따라 올바른 선택을 해야 합니다.

References

[1] "Protection of Aircraft Electrical/Electronic Systems against the Indirect Effects of Lightning, " Advisory Circular AC 20-136B, Federal Aviation Administration, 2011.

본 자료는 다쏘시스템의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : https://r1132100503382-eu1-3dswym.3dexperience.3ds.com/community/swym:prd:R1132100503382:community:39/post?content=swym:prd:R1132100503382:communitypost:HMv6DLSgRrubevyI-kgVKw

관리자

2024.03.25

조회 128

|

|

|

[문서] 낙뢰 간섭 효과 분석 파형

낙뢰 테스트를 위한 이상적인 외부 전류 구성 요소는 Standard 및 항공우주, 방위 관련 문헌에 정의되어 있습니다[1,2,3]

파형 종류

A – 첫 번째 복귀 스트로크

AH – 높은 고도에서의 첫 번째 복귀 스트로크

B – 중간 전류

C – 계속되는 전류

D – 후속 스트로크 중 첫 번째 스트로크

D/2 – 나머지 후속 스트로크 중 하나

H – 리더 개발, 부착 및 분리 과정의 전류 펄스 및 플래시 지속 시간 동안 발생하는 유사한 펄스

직사각형 펄스인 구성 요소 C를 제외한 다른 모든 구성 요소는 낙뢰 전류 구성 요소 A의 그림 1과 같이 상승 및 감쇠 시간이 지정된 비주기적 펄스입니다.

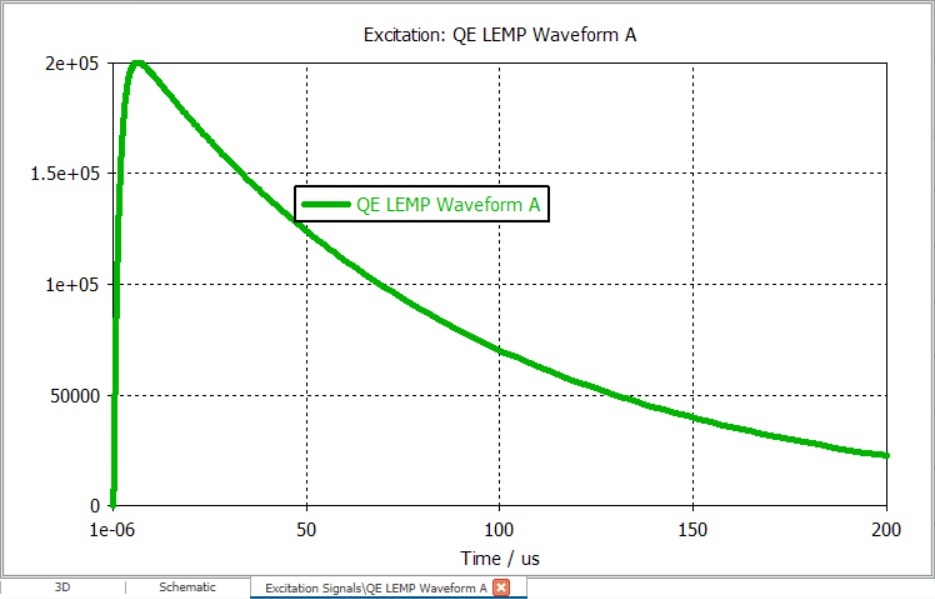

그림 1. 낙뢰 전류 파형 A의 비주기적 펄스

낙뢰 간접 효과에 대한 전자기 시뮬레이션을 위해서는 전류 성분 파형의 닫힌 형태의 표현이 필요합니다. [1]에 지정된 최신 파형은 QE(Quadruple Exponential)입니다:

이전 표준, 특히 MIL-STD [2]에서는 DE(Double Exponential)가 사용됩니다:

QE 파형의 경우 t>0에서의 최대 속도 변화는 실제 낙뢰 전류를 더 현실적으로 표현하며 수치 불안정성을 줄입니다. t=0에서 DE 파형의 첫 번째 도함수는 0과 같지 않고 최대 속도 변화도 같습니다. QE 파형의 추가 마지막 항은 상승 기울기에만 영향을 미칩니다.

CST Studio suite에서 QE 파형은 knowledge base QA00000306492에서 VBA 매크로를 다운로드하여 사용할 수 있습니다. VBA 매크로에 추가하는 방법에 대한 지침도 함께 제공됩니다. 매크로는 로그 시간 척도로 파형 값을 계산하며 오류 제어를 통해 사용자가 지정한 정확도에 도달할 수 있도록 합니다. 그림 2와 같이 앞서 언급한 전류 파형 중에서 선택할 수 있으며 DE 파형으로도 전환할 수도 있습니다. USER 파형을 사용하면 각각 QE 및 DE 낙뢰 펄스의 사용자 지정 사양을 지정할 수 있습니다.

그림 2. VBA 매크로

이 매크로는 3D 및 schematic에서 transient 시뮬레이션을 위해 CST Studio Suite에서 QE 파형을 정의하는데 사용할 수 있습니다. 이 매크로는 ASCII import를 사용하기 때문에 특히 상승 기울기 동안 샘플링이 중요하며 이를 위해 로그 샘플링이 필요하고 구현됩니다. 참고적으로 Excitation 신호를 정의하는 CST Studio Suite의 내장 기능인 “User defined”는 로그 샘플링을 제공하지 않기 때문에 전류 펄스가 주입된 낙뢰 간접 효과 분석에는 이 매크로를 사용하는 것을 추천합니다.

References

[1] "Aircraft Lightning Environment and Related Test Waveforms," SAE ARP5412B (EUROCAE ED-84A), SAE International, 2013.

[2] "Electromagnetic Environmental Effects, Requirements for System," SMIL-Std-464C, Department of Defense, Interface Standard, 2010.

[3] R. J. Perez, "Handbook of Aerospace Electromagnetic Compatibility," Wiley, New Jersey, 2019.

본 자료는 다쏘시스템의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : https://r1132100503382-eu1-3dswym.3dexperience.3ds.com/community/swym:prd:R1132100503382:community:39/post?content=swym:prd:R1132100503382:communitypost:LUtBy3AbReKTrJR04g4Wxg

[Lightning Indirect Effects Analysis Waveforms in A&D, Dassault Systèmes, Marco KUNZE]

관리자

2024.03.22

조회 186

|

|

|

[문서] PCB와 Ground 간 커플링의 EMC Simulation(Using CST)

본 자료에서는 CST Studio Suite®를 사용한 Simulation이 제품의 emission 성능을 개선하는 데 어떻게 도움이 되는지 설명합니다. 인쇄 회로 기판(PCB)의 신호 트레이스와 Ground 사이의 결합은 일반적으로 전자파 적합성(EMC)적 특성으로 이러한 관점이 분석이 필요합니다. 아래 소개된 내용은 Conducted emission에 대해 논의하지만 Radiated emission로 확장할 수 있습니다.

Conducted emission 테스트 배경

Conducted emission(CE) 테스트는 전선의 전류 또는 라인 임피던스 안정화 네트워크(LISN) 측정 포트의 전압을 측정하는 것으로 구성됩니다. 자동차 분야에서 테스트 설정은 테스트 대상 장비(EUT), 전선, LISN, EMI(전자파 간섭) 수신기, CAN과 같은 통신 장치, 부하(필요한 경우) 및 자동차 섀시를 나타내며 전압 기준을 나타내는 Ground으로 구성됩니다.

그림 1은 간단한 테스트 설정을 설명합니다: Vbat 및 GND는 각각 전원 공급 장치의 양극 및 음극용 전선을 나타냅니다. 이 경우의 EUT는 단순한 "인쇄 회로 기판(PCB)"이지만 다른 전기 또는 전자 시스템을 나타낼 수도 있습니다. CE 테스트 중 EMC 성능은 측정된 전압/전류를 자동차 분야에서 가장 많이 적용되는 표준인 CISPR 25와 같은 표준에서 정의한 한계와 비교하는 것으로 구성됩니다. 저희의 경우 전압 방식에 중점을 둡니다. 전압 방식과 전류 방식에 의한 테스트는 동등하기 때문에 측정 방법의 선택은 제한이 없습니다.

Figure 1. Conducted emission 테스트를 위한 EMC 테스트 설정

EUT 설명

이 테스트에서 EUT는 신호에 의해 여기된 하나의 트레이스와 여러 개의 접지층으로 구성된 간단한 PCB입니다. 이를 사용하여 트레이스와 Ground 사이의 결합과 레이아웃이 이 결합에 미치는 영향을 설명합니다. 세 가지 Case를 테스트합니다

Case 1은 2레이어 PCB로 구성됩니다. GND와 트레이스로 구성됩니다. (그림 2 참조).

Case 2는 전파 신호를 위한 두 개의 솔리드 PCB 레퍼런스 레이어 사이에 여기 트레이스가 있는 4레이어 PCB로 구성됩니다(그림 3 참조).

Case 3은 Case 2와 동일하며, 트레이스 바로 아래에 하단 레이어에 구멍이 있습니다(그림 4 참조).

Figure 2. PCB Case 1의 그림, PCB 하단도

Figure 3. PCB Case 2의 그림, PCB 하단도

Figure 4. PCB 케이스 3의 그림, PCB 하단도

실제 해석 진행 시 Case 2와 Case 3은 4개가 아닌 3개 레이어로 단순화되었습니다. 실제로 L4는 모델을 단순화하고 결과 해석을 더 쉽게 하기 위해 억제되었습니다. L3과 L4 사이에는 노이즈 소스가 없고 이들 사이에 존재할 수 있는 전압은 무시할 수 있기 때문에 이러한 단순화는 최종 결과에 영향을 미치지 않습니다. 접지 레이어는 디커플링 커패시터를 통해 연결된 전력 레이어일 수도 있습니다. 이 경우 커패시터는 완벽한 것으로 간주되며 레이어 간 최소 임피던스를 갖기 위해 여러 비아를 사용하여 서로 연결됩니다. 따라서 3개의 레이어를 가진 PCB 모델은 전체 4레이어 시스템을 대표합니다.

PCB는 그림 5에서 볼 수 있듯이 직사각형 형태와 21cm x 10cm의 치수를 가지며, 트레이스 길이는 21cm, 폭은 0.25mm입니다.

Figure 5. PCB 치수 및 트레이스 길이

Conducted emission 테스트 배경

설정은 PCB와 20cm 길이의 와이어를 통해 PCB 레퍼런스를 LISN 임피던스에 연결하는 것으로 구성됩니다. 일반적으로 전원 공급 장치는 음극용 전선과 양극용 전선 두 개를 사용하여 PCB에 연결됩니다. 이 테스트에서는 이러한 전원 공급 장치 와이어를 접지 와이어 하나로만 대체합니다.

이 테스트에서는 커플링의 가장 지배적인 모드인 공통 모드만 고려합니다. 실제로 음극선과 양극선 사이의 입력 임피던스는 무시할 수 있는 수준입니다. 일반적으로 커패시터로 연결되며, 이 테스트에서는 커패시터 연결이 이상적이라고 가정합니다.

테스트 설정의 3D 모델은 그림 6에 나와 있습니다. 보드는 수직 방향으로 배치되어 있고 트레이스는 하단 레이어에 있으며 접지선은 상단 레이어에 연결되어 있습니다. PCB와 Ground 사이에는 로컬 접지 연결이 없습니다.

Figure 6. 테스트 설정의 3D 모델

노이즈 소스 및 종단

트레이스는 버퍼 또는 마이크로 컨트롤러에서 나오는 신호에 의해 여기되고 고정 임피던스에 의해 종단됩니다. 이는 일부 고주파 성분이 있는 클록 또는 통신 신호를 모델링합니다. Simulation에서 여기는 100kHz ~ 300MHz 주파수 범위의 광대역 전압 소스입니다. 종단은 50kΩ 저항입니다. 테스트된 주파수 범위와 관련하여 종단 임피던스의 정확한 값은 중요하지 않지만 용량성 결합을 더 우세하게 만들기에 충분히 높습니다.

Simulation 방법

3D Simulation에는 Frequency Domain(FD) solver가 사용됩니다. 100kHz ~ 200MHz의 주파수 범위에서 PCB를 분석하는 데 가장 적합한 선택입니다. 먼저 FD solver를 사용하여 3D 모델을 구축, 메시화 및 해석합니다. 그런 다음, 3D Simulation 결과를 기반으로 회로 Simulation을 수행하기 위해 CST Studio Suite의 회로도와 공동 Simulation을 사용합니다.

구성은 분석하고자 하는 각 포트에 연결된 임피던스와 구성 요소 측면에서 별도로 정의됩니다. 즉, 매번 3D 모델을 다시 풀지 않고도 종단 및 구동 값을 변경하고 LISN 전압을 얻을 수 있습니다. 따라서 Simulation 시간이 크게 단축됩니다. 또한 공동 Simulation 설계 흐름에서 '결과 결합' 기능을 사용하여 모든 구동 및 종단 회로를 고려하여 3D 모델에서 전류 및 EM 필드를 계산할 수 있습니다. 이 시각화는 조사에 유용합니다. Simulation 된 모든 구성에 대한 결합 프로세스를 심층적으로 분석할 수 있습니다. 테스트된 회로는 간단하며 그림 7에 설명되어 있습니다.

Figure 7. Case 1 "2 레이어" 및 Case 2 "3 레이어" 각각에 대한 Simulation 회로

Simulation Case에서는 GND 와이어가 PCB에 직접 연결되었지만, 많은 설계에서 그렇듯이 “Common mode choke”"와 같은 임피던스를 통해 분리하거나 연결할 수 있다는 점에 유의하세요.

Simulation Results

AC 분석을 사용하여 트레이스가 1V 광대역 노이즈 소스에 의해 여기되었을 때 LISN의 전압을 분석합니다. 얻은 결과는 그림 8에 나와 있습니다. Case 1 "단일 레이어"의 경우 커플링 비율이 78dB이므로 트레이스에 1V를 인가하면 20MHz에서 42dBµV가 발생하며, 이는 CISPR 25 Conducted emission 클래스 5 "협대역 잡음"의 요구 사항보다 높다는 것을 의미합니다. Case 2 "이중 레이어"의 경우 -58dBµV로 감소하며, 이는 매우 낮은 수준입니다. Case 3 "구멍이 있는 트레이스"의 경우 결합 레벨은 25dBµV이며, 이는 Case 2에 비해 83dB 증가한 수치입니다. 실제로 Case 3은 CISPR 25 클래스 5에 따라 Conducted emission의 위험이 높습니다. 전체 결과는 트레이스 위 또는 아래에 있는 접지층에 구멍이 있으면 3~4개의 레이어를 사용하여 얻은 개선 효과를 82dB(-58dBµV에서 25dBµV로) 감소시키는데, 이는 3D Simulation을 사용하지 않으면 추론하기 매우 어려운 수치입니다.

Figure 8: Case 1, Case 2 및 Case 3의 LISN 임피던스에서 계산된 전압

커플링 메커니즘 분석하기

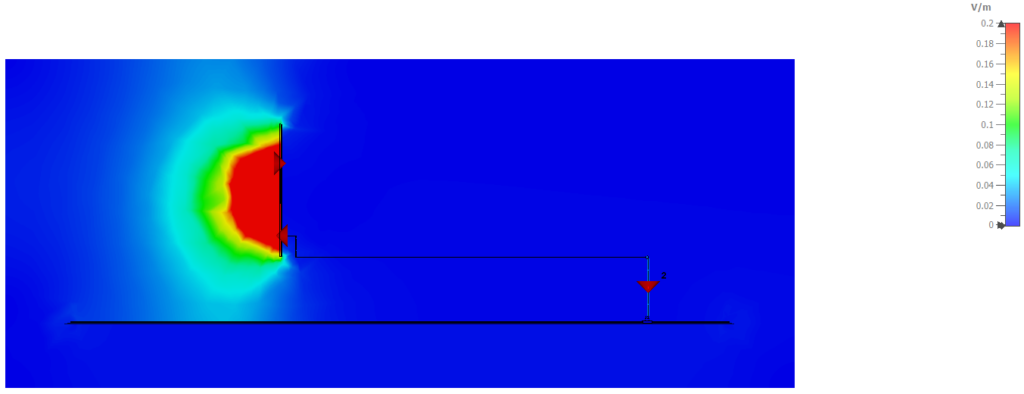

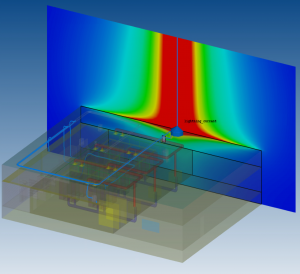

이 시점에서 가장 먼저 떠오르는 질문은 다음과 같습니다: PCB와 Ground 사이에 연결이 하나만 있는데 어떻게 LISN에 전류가 흐를 수 있을까요? 이 질문에 답하기 위해 20MHz에서 E 필드 모니터를 사용할 수 있습니다(그림 9 참조). PCB와 Ground 사이에 전기장이 존재한다는 것을 명확하게 알 수 있습니다. 이 필드의 변화는 그림 10에 표시된 것처럼 PCB와 Ground 사이의 부유 커패시턴스를 통해 변위 전류를 유도합니다. 이 변위 전류는 LISN 임피던스에 전압을 유도합니다.

Figure 9. Case 1의 경우 20MHz에서 필드 모니터

Figure 10. PCB와 Ground 사이의 정전 용량 결합

Case 2와 같이 트레이스가 두 접지층 사이에 매립되면 트레이스와 Ground 사이의 커플링이 크게 감소합니다. 실제로 트레이스와 접지 층 사이의 결합이 크게 증가하여 전류 분포가 내부 레이어 사이에 국한되도록 변경됩니다. 전기장이 트레이스 층과 PCB 층 사이에 국한되므로 PCB 층의 외부 면에는 전류가 흐르지 않고 PCB 층과 Ground 사이에는 전계가 존재하지 않습니다. 이는 PCB와 Ground 사이의 결합을 감소시킵니다.

Figure 11. 커플링 감소 그림

"Case 3"에서와 같이 PCB 레이어에 트레이스 위에 구멍이 있는 경우, 커플링 레벨은 Case 1 "단일 레이어" 그림 12의 레벨에 가까워집니다. 그 차이는 33dB에 불과합니다. 물론 이 값은 구멍의 위치와 크기에 따라 달라집니다.

Figure 12. 세 가지 Case에 대한 20MHz에서의 전기장

결론

3D Simulation을 사용하여 Conducted emission 테스트 설정에서 PCB와 Ground 사이의 결합을 테스트했습니다. 그 결과 높은 임피던스로 종단된 트레이스는 트레이스와 Ground 사이에 전기장을 생성하여 LISN 임피던스에서 변위 전류와 전압을 유도하는 것으로 나타났습니다. 트레이스가 두 개의 내부 레이어 사이에 라우팅되면 이러한 커플링이 크게 감소합니다. 그러나 트레이스 위나 아래에 접지층 중 하나에 구멍이 있으면 이러한 개선 효과가 크게 저하될 수 있습니다. PCB의 짧은 부분 위에 작은 구멍만 있어도 개선 효과가 크게 저하될 수 있다는 놀라운 결론이 나왔습니다. 제안된 Simulation 워크플로우를 사용하면 구동 및 종단 임피던스를 변경하거나 PCB 레이아웃을 수정하는 등의 방법으로 대체 구성을 테스트하는 것이 매우 간단합니다.

본 자료는 다쏘시스템의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : EMC Simulation of the Coupling Between a PCB and a Ground Plane (다쏘시스템, Djamel Guezgouz)

관리자

2024.03.14

조회 149

|

|

|

[문서] ESD (Contact) : Electrostatic Discharge

Dassault Systèmes

ESD란? Electrostatic Discharge (ESD)는 인체와 같이 전하를 띤 두 물체가 서로 contact할 때 정전기가 발생하는 현상입니다. 인체에서 발생하는 고전압 ESD 펄스가 전자기기 내부로 유입되면 기기 내부의 IC 회로를 손상시킬 수 있습니다. ESD 현상은 전자 부품의 작동 속도를 빨라지게 하고 작동 전압을 감소시킵니다. 이는 심각한 간섭문제를 발생시켜 전자 시스템의 손상 및 오작동 또는 고장을 일으킬 수 있어 이를 방지하기 위한 보호 설계가 필수적입니다.

ESD IEC 표준

테스트 결과의 재현성을 보장하기 위해 사용 가능한 대부분의 ESD generator는 IEC 61000-4-2 표준의 사양을 준수합니다. 이 표준은 ESD generator에 의한 주입 파형 교정 절차를 설명합니다. 해석용 ESD gen-erator의 파형 특성은 표준에 문서화된 이상적인 파형 특성과 비교됩니다. 아래 그림 1에 표시된 전류(A) 대 시간(ns)의 플롯은 Contact discharge 모드에서 ESD gen-erator의 이상적인 성능을 나타냅니다. 파형의 동작은 주로 상승 시간에 의해 결정되며 discharge의 첫 번째 피크 전류, 30ns의 전류 및 60ns의 전류에 의해 결정됩니다.

그림1. IEC 61000-4-2 표준에 따른 ESD 전류 파형

ESD 해석을 진행하는 경우 해석용 ESD Generator가 있어야 합니다. 해석용 ESD generator는 IEC 표준에 지정된 다양한 테스트 레벨(예: 2kV, 4kV, 6kV, 8kV , 표 1에 언급)의 결과가 표준에 명시된 성능 요구 사항과 유사하게 도출되는지 비교해보아야 합니다.

표1. IEC 61000-4-2 표준에 따른 contact discharge 전류 파형 파라미터

목적

ESD 표준에 근접하게 성능을 맞추기 위한 다양한 ESD generator 설계 연구가 이미 수행되었지만, 하위 구성 요소를 사용한 ESD generator 성능 튜닝에 관한 정보는 거의 없습니다. 이 백서에서는 시뮬레이션을 통해 다양한 ESD generator 설계 파라미터를 변경하고 그 효과에 대해 기술 합니다.

ESD generator 성능은 표준에 명시된 요구 사항과 비교하여 검증되며 다양한 출판물의 측정 결과와 추가 비교하여 검증하였습니다.

ESD 테스트 방법

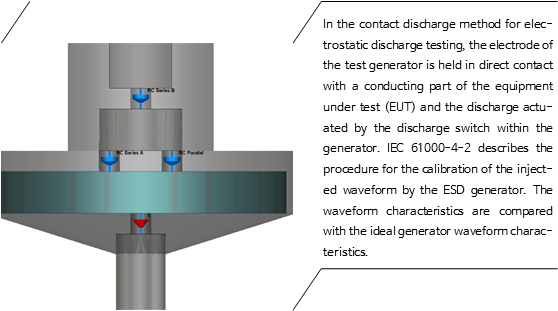

이 표준은 contact discharge 및 Air discharge이라는 두 가지 ESD 테스트 방법을 정의합니다. contact discharge 방식에서는 테스트 generator의 전극이 테스트 대상 장비의 전도성 부분과 직접 contact한 상태로 유지됩니다. Air discharge 방식에서는 테스트 generator의 전극을 EUT에 가깝게 가져와서 전극과 EUT 사이에 아크가 형성되어 discharge가 발생합니다.

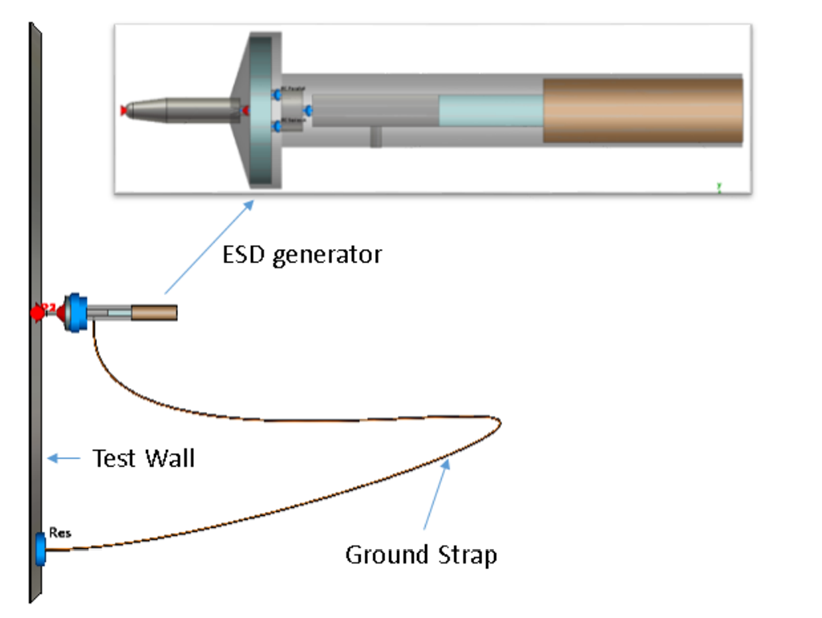

그림 2. ESD Gun model

Contact discharge을 위한 ESD generator 모델

ESD generator는 일반적으로 일반적인 human body discharges 를 재현하는데 사용됩니다.

정확하고 효율적인 3D 모델링과 generator의 메시화는 중요한 측면입니다.

ESD generator의 실제 설계는 복잡하기 때문에 이에 상응하는 단순화된 3D 모델을 다쏘시스템에서 개발하여 고객에게 제공하고 있습니다. ESD generator 모델에는 다양한 금속 및 유전체 부품이 포함되어 있으며, Lumped element 및 Excitation용 포트가 포함되어 있습니다.

그림 2에서 볼 수 있듯이 제공되는 해석용 ESD generator는 2m 접지 스트랩이 포함된 ESD generator로 1.2m x 1.2m 금속 벽에 배치됩니다. 이를 통해 IEC 표준에 정의된 캘리브레이션 구성에 따라 CST Studio Suite에서 시뮬레이션하여 동작을 연구하고 성능을 검증합니다. 그림 3은 IEC ESD 표준 파형에 유사하게 시뮬레이션 된 ESD generator 모델의 팁 전류를 보여줍니다.

그림 3. 설계된 ESD generator의 contact discharge 전류 파형

그림 4. 다양한 discharge 전압 레벨에 대한 contact discharge 전류 파형

팁 설계, 접지 스트랩 형상, 스트랩 인덕턴스 등과 같은 특정 파라미터를 조정하여 ESD generator의 전류 특성이 규정에 만족되도록 수정해 볼 수 있습니다. 이러한 주요 파라미터 중 일부는 다음 섹션을 통해 설명하겠습니다.

접지 스트랩 두께의 영향

ESD 표준에 따라 ESD generator에는 2m 길이의 접지 케이블이 장착되어 있으며, 이는 discharge 전류의 복귀 경로를 제공합니다. ESD 표준은 접지 스트랩의 두께 또는 직경에 대한 기준 값을 지정하고 있지 않으나 이 영향성에 대한 역할을 이해하는 것은 중요합니다. 그 이유는 이러한 특성이 전체 인덕턴스에 직접적으로 기여하고 discharge 파형에 영향을 미치기 때문 입니다. 이론적으로 스트랩의 self 인덕턴스는 길이, 직경과 같은 물리적 파라미터에 의해 제어됩니다. 이러한 특성을 시뮬레이션해 보았을 때 그림 5에서 볼 수 있듯이 partial 인덕턴스는 스트랩 반경에 반비례합니다.

그림 5. 다양한 반경에 대한 저주파에서 접지 스트랩의 partial 인덕턴스

그림 6. 다양한 스트랩 반경에 대한 contact discharge 전류 파형

이 백서에서 평가한 ESD generator 접지 스트랩의 길이는 약 2m입니다. 그림 6에서 볼 수 있듯이 첫 번째 피크 이후의 ESD generator discharge 성능은 self 인덕턴스의 변화로 인해 스트랩 반경에 영향을 받습니다. 특히 ESD 파형의 두 번째 피크를 이동시키는 데 중요한 역할을 합니다.

접지 스트랩 길이의 효과

ESD 표준에 따라 캘리브레이션에 필요한 접지 스트랩의 최소 길이는 2m이며, 이 길이가 충분하지 않은 경우 표준에 맞게 성능을 맞추기 위해 길이를 최대 3m까지 연장할 수 있습니다. 접지 스트랩의 길이는 루프 인덕턴스로 인해 두 번째 피크의 위치에 영향을 줍니다.

일부 간행물에서는 전기적으로 길이를 늘리기 위해 접지 스트랩과 직렬로 lumped element를 추가하여 더 짧은 접지 스트랩을 사용하는 방법을 제안합니다. 일부 상황에서는 이 근사치가 합리적일 수 있지만, 일반적으로는 접지 스트랩의 실제 길이를 모델링하여 전자기장 및 discharge 파형에 미치는 영향을 분석합니다.

그림 7에서 볼 수 있듯이, partial 인덕턴스는 낮은 주파수에서 접지 스트랩 길이에 정비례합니다.

그림 7. 다양한 스트랩 길이(mm)에 대한 저주파에서 접지 스트랩의 partial 인덕턴스

그림 8에서 접지 스트랩의 길이를 3m로 늘리면 첫 번째 피크 이후의 ESD 파형에서 링잉이 감소합니다.

그림 8. 다양한 스트랩 길이(mm)에 대한 Contact discharge 전류 파형

접지 스트랩의 길이가 길어지면 리턴 경로에서 루프 인덕턴스가 증가하여 생성된 ESD의 두 번째 피크에서 이상적인 값(표준)과의 편차가 줄어듭니다.

접지 스트랩 형상이 partial 인덕턴스에 미치는 영향

실제 ESD 테스트 중에 접지 스트랩이 다른 경로를 따라 다른 루프 구성을 형성할 수 있습니다. 그 중 일부는 그림 9에 나와 있습니다. 이러한 스트랩의 형상이 궁극적으로 루프에 영향을 미치는데 특히 첫 번째 피크 이후의 ESD discharge 프로파일에 영향을 미치게 됩니다. 이러한 인덕턴스 특성과 같은 분석은 CST Studio Suite의 Partial RLC solver를 사용하여 수행할 수 있습니다. 이렇듯 해석을 통해 접지 스트랩의 형상 특성을 관찰하고 사용자는 가상 물리적 테스트를 통해 사용할 접지 스트랩의 모양을 결정할 수 있습니다.

그림 9. 다양한 루프 구성에 대한 접지 스트랩의 partial 인덕턴스

접지 스트랩과 ESD generator 사이의 인덕턴스 합산 효과

그림 10. ESD generator와 접지 스트랩 사이의 Lumped element

접지 스트랩 길이의 제한으로 인해 ESD generator의 전체 인덕턴스를 제어하기 어려울 수 있습니다.

또한 길이를 연장하면 더 많은 링잉이 발생할 수 있습니다. 따라서 이러한 제한을 극복하기위해 인덕턴스(예 1nH의 인덕턴스) 소자를 접지 스트랩과 ESD generator 사이에 연결하면 이러한 문제를 완화할 수 있습니다. 이 직렬 인덕턴스 값은 접지 스트랩에 추가되어 전체 인덕턴스 값의 증가를 야기합니다. 따라서 추가되는 값을 신중하게 선택해야 합니다. 물리적 ESD generator에서는 각 테스트에 대해 일괄 소자 값을 조정하는 것은 실용적이지 않습니다. 그러나 시뮬레이션은 원하는 경우 얼마든지 변경해 볼 수 있기때문에 해석을 통해 적합한 값을 결정할 수 있습니다. 이 문서의 모델은 그림 10에 표시된 접지 스트랩과 ESD generator 사이에 1nH 인덕터를 사용합니다. 이를 이용 시 케이블 길이와 generator 성능 간의 좋은 균형을 보여줍니다. 그림 11은 이에 대해 테스트 진행해본 내용으로 더 높은 인덕턴스 값을 추가하면 파형에 심각한 영향을 미치며, 이는 ESD generator에 대한 IEC 표준 사양을 위반할 수 있음을 확인 할 수 있습니다. 따라서 적절한 값의 선택이 중요하며, 본 모델은1nH 인덕터를 사용할 때 ESD 파형의 동작은 IEC 표준과 거의 일치합니다.

그림 11. 다양한 스트랩 인덕턴스 값에 대한 contact discharge 전류 파형

테스트 설정 시 ESD generator 동작

UT를 사용하여 ESD generator를 검증하기 전에 그림 12와 같은 테스트 설정을 통해 동작을 연구합니다. 테스트 셋업은 CST Studio Suite를 사용하여 IEC 61000-4-2 표준의 지침에 따라 모델링 됩니다. discharge 저항 와이어의 양쪽 끝에 사용되는 블리드 저항은 ESD를 점차적으로 제거합니다.

그림 12. ESD generator와 테스트 셋업

4kV 입력 전압에 대한 ESD 발생기의 동작은 그림 13과 같이 EUT 없이 모니터링됩니다. ESD generator의 초기 응답 및 초기 피크가 표준 모델과 유사했습니다. 다만 셋업이 있는 경우 discharge 프로파일의 "tail"에만 변동이 있음을 알 수 있습니다. 따라서 가상 테스트 평면 위에 EUT를 배치하고 접지면과 블리드 저항 와이어를 제외할 수 있습니다.

그림 13. ESD generator의 동작

측정 결과를 통한 검증

측정 결과를 통해 설계된 ESD generator를 검증하기 위해 2003년 IEEE 전자파 적합성 심포지엄(IEEE Symposium on Electromagnetic Compatibility)의 논문집에 실린 "ESD excitation model for susceptibility study"을 참조했습니다[Ref]. 그림 14에서 CST Studio Suite를 사용한 모델의 단면도를 볼 수 있습니다. 이 접근 방식에서 ESD generator는 중앙에 직사각형 슬롯이 있는 금속 인클로저에 contact discharge됩니다. 중앙에 위치한 사각형 루프에 인클로저 내부와 상단 중앙에 위치한 사각형 루프에서 유도된 전압이 기록되며 이를 해석과 측정 결과 비교를 통해 검증해 보았습니다.

1kV discharge에 대한 측정이 수행되었으므로 시뮬레이션에서도 유사한 조건이 설정되었습니다. 그림 15는 메탈 루프에 유도된 전압을 보여줍니다. 이때의 동작특성은 정현파 동작을 보이며, 이 이유는 슬롯의 길이가 ½ 파장에 해당하는 주파수에서 공진하기 때문입니다. 시뮬레이션 및 측정데이터는 잘 일치합니다.

그림 14. 금속 인클로저로 discharge하는 ESD generator

그림 15. 처음 10초동안 밀폐된 사각 루프에서 유도되는 전압

그림 16과 17에서 볼 수 있듯이 ESD generator 팁 전류와 스트랩 전류는 시뮬레이션 결과와 측정 결과 간에 어느정도 좋은 일치도를 보여줍니다.

그림 16. ESD generator의 팁 전류

그림 17. ESE generator의 스트랩 전류

시뮬레이션은 Surface current 시각화를 통해 전류 분포와 강도에 대한 통찰력을 얻을 수 있습니다.\

그림 18. 슬롯으로 인한 박스 및 루프 내부의 Surface current

그림 18은 1GHz 주파수에서 Surface current 를 플롯 한 것입니다. ESD generator 팁에서 인클로저까지의 전류 리턴 경로 및 수평 슬롯 주변, 접지 스트랩을 통해 다시 돌아오는 전류 리턴 경로를 명확하게 볼 수 있습니다. 또한 Surface current 위상에 애니메이션을 적용하여 시간변화에 따른 전류 흐름을 시각화 할 수 있습니다.

수평 및 수직 커플링 평면으로의 discharge

간접 discharge에 대한 ESD generator 모델의 견고성을 테스트하기 위해 수평 결합면(HCP)과 수직 결합면(VCP)으로 구성됩니다. mouse cable를 나타내는 와이어가 VCP 근처에 배치됩니다. 그림 19에 표시된 테스트 설정 및 측정 값은 2003년 IEEE Symposium on Electromagnetic Compatibility에서 발표된 다음 컨퍼런스 논문, "ESD excitation model for susceptibility study"에서 가져온 것입니다.

그림 19. 수평 및 수직 결합면 설정

Mouse cable의 가까운 끝에서 유도된 전압의 측정 및 해석 결과를 서로 다른 시나리오로 비교해 보았습니다. 그림 20는 50옴 저항을 사용하여 VCP가 HCP로 종단되지 않은 경우의 결과입니다. 그림 21은 50옴 저항을 사용하여 VCP가 HCP로 종단된 경우의 결과입니다.

그림 20. VCP가 50ohm으로 중단되지 않았을 때

mouse cable의 가까운 끝에서 유도된 전압

그림 21. VCP가 50ohm으로 중단되었을 때

mouse cable의 가까운 끝에서 유도된 전압

스마트폰 기기의 가상 ESD 테스트

스마트폰 모델을 테스트 평면 위에 놓고 전도성 본체에 contact discharge을 수행하여 ESD 민감성을 테스트해보았습니다. 이때 두 가지 다른 discharge 위치에 대해 진행하였습니다. 첫 번째는 충전 슬롯 커넥터 쉴드이고 다른 하나는 금속 프레임 링입니다.

그림 22. 휴대폰 금속 프레임의 contact discharge

그림 22는 ESD 해석 예제로 generator의 8kV ESD를 인가하여 스마트폰의 외부 금속 프레임에 contact discharge을 인가 합니다. 이는 ESD에 의해 내부로 유기된 전류가 표준 USB 전류 제한을 초과할 경우 스마트폰 내부의 IC를 손상시킬 수 있기 때문에 이를 모니터링하기 위해 그림 23과 같이 IC 핀의 전류 레벨을 관찰한 내용입니다. 그림 24에 이 결과를 나타내었으며, 확인된 전류 레벨은 USB 표준에 지정된 전류 제한보다 훨씬 낮았습니다.

그림 23. 유도 전류의 효과가 기록되는 PCB 포트

그림 24. 8kV의 contact discharge로 인한 포트 편의 전류 레벨

실제 ESD 테스트 중에 EUT는 다양한 방향으로 회전하고 EUT의 다양한 테스트 지점에 ESD 신호를 인가합니다. 이러한 의미에서 그림 25에서 볼 수 있듯이 스마트폰의 충전 슬롯 커넥터에 contact discharge ESD 테스트를 수행하였습니다. 그림 26은 그 결과로 내부 IC 핀의 유도 전류 레벨로 표준 USB 전류 제한보다 낮습니다.

그림 25. 휴대폰의 충전 핀 커넥터 쉴드에 contact discharge가 발생

그림 26. 충전 핀 커넥터 실드에서 8kV의 contact discharge로 인한 포트 핀의 전류 수준

결론

ESD는 전자 제품 분야에서 매우 중요한 현상입니다.

CST를 이용한 해석진행시 시장에 제품을 출시하기전 3D ESD 시뮬레이션을 통해 EUT에 미치는 악영향을 예측할 수 있습니다. 이를 위해 일반적인 ESD generator의 단순화된 모델이 CST Studio Suite용으로 개발되었으며 이를 통해 ESD 전류 및 필드 응답을 정확하게 시뮬레이션 할 수 있습니다. 앞서 안내된 내용과 같이 제공되는 ESD generator의 다양한 요소가 성능에 미치는 영향을 분석할 수 있으며 이를 기반으로 IEC 표준과 일치시킬 수 있습니다. CST에서 제공하는 ESD Generator를 이용하여 시뮬레이션을 많은 현업에서 진행하고 있으며, 해석을 통한 가상프로토타입의 결과는 측정값과 우수한 정확도를 보이고 있습니다. 또한 해석의 가장 큰 장점은 전자기장의 시각화를 통해 문제에 대한 통찰력을 얻어볼 수 있는 것입니다. 해석의 가상 프로토 타입을 통한 ESD 분석을 통해 제품 출시까지의 샘플 제조기간 및 비용 절감, 통찰력을 통한 제품 개발기간을 혁신적으로 줄여볼 수 있습니다.

* 본 자료는 Dassault systems 의 ELECTROSTATIC DISCHARGE Contact의 번역본입니다.

* 본 자료는 다쏘시스템 홈페이지 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

- 원본 : 다쏘시스템

관리자

2023.09.26

조회 518

|

|

|

[문서] 분산 스펙트럼 클럭 생성을 고려한 DCDC 컨버터 시뮬레이션

Dassault Systèmes

CST Studio Suite 시뮬레이션을 사용하여 DCDC 컨버터의 전자파 적합성(EMC) 성능을 예측하는 방법을 소개합니다. 시뮬레이션에서 분산 스펙트럼 클럭(SSC: Spread Spectrum Clock) 생성 및 EMI 수신기를 고려하면 보다 현실적인 결과를 얻을 수 있습니다.

배경 지식

이름에서 알 수 있듯이 DCDC 컨버터는 DC 전압을 다양한 레벨로 변환하는데 사용되는 전자 시스템 그룹입니다. DCDC 컨버터는 거의 모든 전자 제품에서 찾을 수 있습니다. DC 전원을 고효율로 변환하기 위해 SMPS(스위치 모드 전원 공급 장치, Switch-Mode Power Supply) 개념이 사용됩니다. 그러나 설계 프로세스가 EMC를 고려하지 않은 경우 SMPS는 전자파 적합성(EMC)에 문제를 일으킬 수 있습니다. 전도성 방출(CE, Conducted Emission) 및 방사성 방출(RE, Radiated Emission) 완화를 모두 설계 프로세스에 포함시켜야 합니다.

전도성 방출의 경우 스위칭에 의해 생성된 고주파 노이즈가 주 전원 공급 장치에 결합되어 EMC 표준에 따라 수 kHz에서 최대 수백 MHz까지 측정됩니다. 예를 들어, 자동차 EMC 표준인 CISPR-25에 따른 CE 측정 주파수 범위는 150kHz에서 108MHz 사이입니다. 방사 방출의 경우 PCB에서 발생하는 방출은 일반적으로 3m 거리에 배치된 수신기 안테나에 의해 확인됩니다.

SMPS의 방사는 전력선 케이블에 결합된 노이즈 뿐만 아니라 최적이 아닌 스위칭 노드 루프를 생성하는 열악한 PCB 레이아웃 라우팅으로 인해 발생할 수 있습니다. RE 측정 주파수 범위는 일반적으로 30MHz에서 최대 수 GHz까지입니다. 일반적으로 노이즈를 줄이고 EMC 표준을 준수하려면 레이아웃 및/또는 필터링 구성 요소를 최적화해야 합니다.

분산 스펙트럼 클럭 기술은 전력 전자 어플리케이션, 특히 DCDC 컨버터에 널리 사용되어 왔기 때문에 이 기술을 적용하기 위해 부품이나 레이아웃을 수정할 필요가 없습니다. 레귤레이터 드라이버가 이 기술을 지원하는지 확인하기만 하면 됩니다.

DCDC 컨버터의 회로 시뮬레이션

아래 그림은 DCDC 부스트 비동기 컨버터의 일반적인 회로를 보여줍니다.

그림 1. DCDC 부스트 비동기 컨버터의 일반적인 회로도

노란색 블록은 트랜지스터의 스위칭을 제어하는 포트입니다. 다이오드 모델은 SPICE 블록으로 가져옵니다. 제어 신호는 주기적인 직사각형 펄스로 n-MOSFET 트랜지스터를 스위칭합니다. 스위칭 주파수는 580mA로 17.5V DC 출력 전압을 달성하기 위해 36% 듀티 사이클의 1.25MHz로 고정되어 있습니다. 12V DC 라인이 n-MOSFET 트랜지스터의 코일 및 드레인 핀과 연결되어 있음을 알 수 있습니다. 트랜지스터의 스위칭 “ON” 기간 동안 n-MOSFET의 드레인 핀에 연결된 주 전원 라인은 주기적으로 GND로 내려갑니다. 따라서 이 노드를 스위칭 노드라고 하며 고주파에서 EMC에 강한 영향을 미칩니다.

Transient 시뮬레이터를 사용하여 DCDC 컨버터를 시뮬레이션합니다. 트랜지스터의 transient 스위칭 동작이 시뮬레이션되며 일반적으로 load 전압이 필요한 DC 전압 레벨에 도달한 후 시뮬레이션이 중지됩니다. 배터리 입력의 스위칭 노이즈 스펙트럼은 LISN(Line Impedance Stabilization Network, 라인 임피던스 안정화 네트워크)를 사용하여 기록됩니다. 이상적인 회로 소자를 시뮬레이션한 이 특정 예제에서 LISN의 노이즈는 주로 그림 2와 같은 sinusoidal 파형을 갖습니다.

그림 2. LISN에서 노이즈

사인파와 매우 유사하지만, 이 파동에는 고조파 성분이 있습니다. LISN 스펙트럼은 더 높은 고조파 주파수의 지속적인 감쇠를 보여줍니다. 아래 그림 3은 이 변환기의 LISN 스펙트럼을 보여줍니다.

그림 3. LISN 스펙트럼

그림 3에서 스위칭 주파수의 피크와 더 높은 고조파를 명확하게 볼 수 있습니다. 스위칭 주파수가 1.25MHz로 고정되어 있기 때문에 이 주파수에서 날카로운 피크를 볼 수 있습니다.

LISN에서 이 진폭을 줄이기 위해 트랜지스터에서 제어된 신호 스위칭에 분산 스펙트럼 기법을 적용합니다.

분산 스펙트럼 클럭 생성(SSCG)

SSCG의 기본 아이디어는 고정된 스위칭 주파수를 사용하는 대신 스위칭 신호에 변조를 적용하는 것입니다. 트랜지스터의 스위칭 주파수는 고정된 변조 주파수(fm)와 진폭을 갖는 변조 신호로 변조됩니다. 일반적으로 신호는 삼각형 함수를 사용하여 변조됩니다. 이 삼각형 신호의 진폭에 따라 스위칭 주파수가 공칭 주파수(fc)에서 얼마나 변화하는지가 결정됩니다. 이를 확산률(d)이라고 하며 일반적으로 백분율로 표시됩니다.

스위칭 주파수가 공칭 주파수보다 높은 주파수로 변경되는 경우 “up spreading”이라는 용어가 사용됩니다. 마찬가지로 공칭 주파수보다 낮은 주파수로 변화하는 경우 이 과정을 “down spreading”이라고 합니다. 마지막으로 스위칭 주파수가 대칭적으로 양방향으로 변화하는 경우 “center-spreading”이라는 용어가 사용됩니다. 더 자세한 내용은 그림 4, 그림 5, 그림6을 참조하시기 바랍니다.

그림 4. Up-spreading이 있는 SSCG

그림 5. Down-spreading이 있는 SSCG

그림 6. Center-spreading이 있는 SSCG

분산 스펙트럼을 고려한 DCDC 컨버터 시뮬레이션

CST Studio Suite®로 DCDC 컨버터를 시뮬레이션할 때 트랜지스터를 제어하는 스위칭 신호의 분산 스펙트럼 변조도 고려할 수 있습니다. 이를 통해 설계자는 확산 스펙트럼 기법이 실제 제품에도 적용될 경우 측정 결과에 더 가까운 보다 현실적인 결과를 얻을 수 있습니다.

분산 스펙트럼을 고려하기 위해 CST Studio Suite에는 스위칭 신호 속성과 SSCG 속성을 정의하는 매크로가 포함되어 있습니다. SSCG 매크로는 CST Studio Suite® 2023 schematic editor의 Post-Processing → EMC Workflow → Spread Spectrum Clock Generation에서 찾을 수 있습니다. 분산 스펙트럼 특성은 일반적으로 시뮬레이션된 컨버터의 데이터시트에서 얻을 수 있습니다. DCDC 컨버터의 경우 확산 속도는 일반적으로 6%에서 최대 10% 범위입니다. 그림 7은 이 매크로의 사용자 인터페이스를 보여줍니다.

그림 7. 분산 스펙트럼 매크로 창

매크로는 transient 시뮬레이션 task를 생성하고 분산 스펙트럼 신호를 트랜지스터의 스위칭을 제어하는 포트에 할당합니다(그림 1 참조).

이 transient simulation task를 실행하면 여러 시간 신호 결과를 사용할 수 있습니다. 이 예에서는 LISN의 시간 신호 결과가 그림 8에 나와 있습니다. 스위칭 주파수가 삼각형 신호로 변조됨에 따라 전력선에 결합된 노이즈도 변조 모양에 해당하는 envelope를 나타냅니다.

그림 8. SSCG가 적용된 LISN 시간 신호

푸리에 변환 및 윈도우 함수

주기적 신호의 스펙트럼은 푸리에 변환을 사용하여 계산됩니다. 주기적 신호는 푸리에 급수로 나타낼 수 있으며 이 주기적 신호의 스펙트럼은 서로 다른 주파수 지점에서의 Dirac 펄스로 표시됩니다. 실제 어플리케이션에서 우리는 종종 유한 길이의 신호를 처리합니다. 이 신호의 주기성을 가정하기 위해 푸리에 변환을 수행하기 전에 time gating 혹은 widowing을 적용합니다.

가장 간단한 형태의 time gating 혹은 widowing은 uniform 혹은 box car 윈도우 함수입니다. 그러나 이 윈도우 함수는 스펙트럼에서 높은 사이드 로브 레벨을 생성합니다. 이러한 사이드 로브의 출현을 스펙트럼 누설이라고도 합니다. 높은 사이드 로브 레벨을 줄이기 위해 non-rectangular 윈도우 함수를 적용할 수 있습니다. 여러 가지 윈도우 함수를 CST Studio Suite®에서 사용할 수 있으며, 그림 9는 지원되는 모든 윈도우 함수의 관련 스펙트럼을 보여줍니다.

그림 9. 다양한 윈도우 기능의 스펙트럼

Resolution Bandwidth (RBW)

일반적으로 균일 윈도우 함수의 스펙트럼은 메인 로브가 가장 좁지만 사이드 로브가 높은 반면, 가우시안 윈도우과 플랫 탑 함수는 메인 로브는 넓지만 사이드 로브는 매우 낮습니다(그림9). 표준 CISPR-16은 윈도우 함수 스펙트럼에 대한 마스크 허용 오차를 지정합니다. 허용 오차 마스크 내에 있는 한 모든 윈도우 함수를 사용할 수 있습니다. 대부분의 EMC 어플리케이션에서는 가우시안 윈도우 함수의 스펙트럼이 허용 오차 마스크 내에 위치하기 때문에 가우시안 윈도우 함수가 사용됩니다.

그림 10. CISPR-16 표준에서 가져온 허용 오차 마스크와 CST Studio Suite®의 가우시안 윈도우 함수의 스펙트럼 플롯

윈도우 함수의 너비에 따라 주파수 resolution이 결정됩니다. 이를 RBW이라고 합니다. 당연히 윈도우 폭이 넓을수록 RBW가 작아집니다. 따라서 더 높은 주파수 resolution을 얻을 수 있습니다. 또한 CISPR-16 표준은 다양한 주파수 대역에 대해 측정 중에 적용될 RBW를 지정합니다.

Fstart

Fstop

RBW

CISPR-Band

9 kHz

150 kHz

200 Hz

A

150 kHz

30 MHz

9 kHz

B

30 MHz

1GHz

120 kHz

C/D

1 GHz

18 GHz

1 MHz

E

표 1. 해당 RBW가 있는 CISPR 대역

마지막으로 시간 신호가 윈도우링된 후 최종 스펙트럼을 얻기 위해 푸리에 변환을 적용합니다.

EMI receiver Template-Based Post-processing

분산 스펙트럼을 시뮬레이션에 사용하는 경우, 이 신호의 스펙트럼은 푸리에 변환을 한 번만 계산하여 계산해서는 안되며 시간 창에 걸쳐 여러 번 푸리에 변환을 수행해야 합니다. 이는 주로 시간에 따른 스위칭 주파수의 변화(그림 8 참조) 때문이며 최종 스펙트럼에서 이를 고려해야 합니다. 따라서 분산 스펙트럼 신호의 스펙트럼을 계산하기 위해 EMI receiver template-based post-processing이 사용됩니다.

EMI receiver template 구현은 고속 푸리에 변환(Fast Fourier Transform, FFT) 방법을 사용한 EMI receiver 측정을 기반으로 합니다. 이 수신기에는 CISPR-16 사양을 준수하는 사전 정의된 RBW 및 윈도우 함수 설정이 있습니다. FFT 기반 수신기는 신호에 대한 윈도우 함수의 시프팅을 수행합니다. 각 윈도우 함수 간의 시프트는 신호의 불확실성을 포착하기 위해 약 90%가 겹칩니다. 이러한 시프트된 각 윈도우에 대한 푸리에 변환이 이후에 수행됩니다. 이렇게 하면 여러 스펙트럼 결과가 생성됩니다.

마지막 단계에서 이러한 스펙트럼은 감지에 입력되어 최종 스펙트럼을 얻습니다. 측정과 마찬가지로 EMI receiver template은 “Peak”, “Quasi-Peak” 및 “AVG”의 세 가지 감지기를 지원합니다. 그러나 EMI receiver template은 기본적으로 “Peak” 및 “AVG” 감지기를 사용합니다. “Quasi-Peak” 감지기는 수동으로 활성화할 수 있으며 계산 시간이 더 오래 걸립니다. “Peak” 결과는 각 주파수 지점에서 피크 값을 감지하여 얻어지는 반면 “AVG” 결과를 각 주파수 지점에서 평균을 구합니다. 그림 11은 EMI receiver template의 대화창을 보여줍니다. SSCG 매크로와 마찬가지로 EMI 수신기 템플릿은 CST Design Studio에서 Post-processing → EMC workflow → EMI receiver를 통해 액세스할 수 있습니다.

그림 11. EMI Receiver template 대화 상자

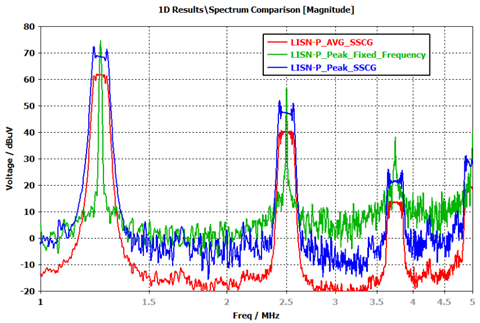

고정 스위칭 주파수와 SSCG의 스펙트럼 비교는 다음 그림 12에서 확인할 수 있습니다. 분산 스펙트럼 기술은 스위칭 주파수를 변경하기 때문에 SSCG를 사용하여 수신한 스펙트럼은 고정 스위칭 주파수를 사용하는 스펙트럼보다 더 넓습니다. 폭은 확산 속도에 해당합니다. 분산 스펙트럼 기술은 또한 고정 스위칭 주파수의 진폭보다 낮은 진폭을 생성합니다. AVG 감지기를 사용하면 진폭이 상당히 감소하는 것을 볼 수 있습니다. 이 예에서는 고정 스위칭 주파수를 사용하는 스펙트럼에 비해 약 13dB 더 낮습니다.

그림 12. SSCG와 고정 스위칭 주파수 간의 스펙트럼 비교

요약

분산 스펙트럼 클럭 생성은 EMC 시뮬레이션 CST Studio Suite®에서 고려할 수 있습니다. 이 기술을 사용하면 레이아웃이나 부품을 수정하지 않고도 노이즈 스펙트럼의 크기를 줄일 수 있습니다. 또한 SSCG는 다양한 시간 신호 결과를 생성하므로 보다 현실적인 최종 스펙트럼을 얻기 위해 EMI receiver template을 적용해야 한다는 점도 중요합니다. CST Studio Suite 시뮬레이션에서 이 두 가지 기능을 모두 고려하면 설계자가 측정 시스템에 더 가까운 보다 현실적인 결과를 얻을 수 있습니다.

본 자료는 다쏘시스템의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

- 원본 : 다쏘시스템

관리자

2023.09.25

조회 292

|

|

|

[문서] ESD (Air) - Electrostatic Discharge

Dassault Systèmes

ESD란? 정전기 방전(ESD)은 인체와 같이 전하를 띤 두 물체가 서로 접촉할 때 정전기가 발생하는 현상입니다. 인체에서 발생하는 고전압 ESD 펄스가 전자 기기에 닿으면 전자 기기에 유입되어 기기 내부의 IC 회로를 손상시킬 수 있습니다. 이러한 ESD 현상은 전자 부품의 작동 속도가 빨라지고 전자 부품의 작동 전압이 감소시킴으로써 심각한 간섭문제를 발생시켜 전자 시스템의 손상, 오작동 또는 고장을 일으킬 수 있습니다.

ESD IEC 표준

테스트 결과의 재현성을 보장하기 위해 사용 가능한 대부분의 ESD generator에는 IEC 61 000-4-2 표준의 사양을 준수합니다. 이 표준은 ESD generator에 의한 주입 파형 교정 절차를 설명합니다. 파형 특성은 ESD generator의 파형 특성은 표준에 문서화된 이상적인 파형 특성과 비교됩니다. 아래 그림 1에 표시된 전류(A) 대 시간(ns)의 플롯은 Contact discharge 모드에서 ESD generator의 이상적인 성능을 나타냅니다. 파형의 동작은 주로 상승 시간에 의해 결정되며 방전의 첫 번째 피크 전류, 30ns의 전류 및 60ns의 전류에 의해 결정됩니다.

그림 1. IEC 61000-4-2 표준에 따른 ESD 전류 파형

목적

Air discharge는 절연 플라스틱이나 스마트폰의 유리 커버와 같이 전도성 부품이 노출되지 않는 경우에 사용됩니다. Air discharge가 생성 시 ESD generator 끝과 테스트 대상 디바이스 사이에 Arc가 형성됩니다. 이렇게 발생된 방전 전류 상승 시간 및 피크 진폭은 Arc 방전 경로 길이에 따라 달라집니다. Arc 경로 길이는 습도 및 generator가 DUT에 접근하는 속도에 따라 달라집니다. 이 백서에서는 선형 ESD generator 전파 모델과 비선형 Arc 모델을 결합하여 Air discharge 모드에서 전류와 전계를 시뮬레이션하는 방법을 제안합니다. ESD generator를 설계하고 CST Studio Suite 과도 TLM 솔버를 사용하여 다양한 구성에 대해 동작을 평가합니다.

ESD 테스트 방법

ESD 테스트 방법이 표준은 Contact discharge 및 Air discharge이라는 두 가지 ESD 테스트 방법을 정의합니다.

Con-tact discharge 방법에서 테스트 generator의 전극은 테스트 중인 장비(EUT)의 노출된 도체와 접촉하고 generator 내의 방전 스위치에 의해 작동되는 방전입니다. Contact discharge 전류는 테스트 및 인증 프로세스의 재현성을 가능하게 합니다. Air discharge 방식에서는 테스트 generator의 충전된 전극을 DUT에 가깝게 가져가 스파크에 의해 장치에 방전이 작동합니다.

IEC 61000-4-2 표준은 도체가 노출되지 않아 Contact discharge이 불가능한 경우 Air discharge 테스트를 채택합니다. 그러나 이 테스트 모드는 Contact discharge 테스트보다 재현성이 떨어집니다.

이 백서에서 ESD generator 테스트 설정은 SIMULIA CST Studio Suite를 사용하여 모델링되었으며 시뮬레이션은 IEC 표준에 명시된 Air discharge에 대한 다양한 테스트 레벨 (예 : 2kV, 4kV, 8kV)에 대해 수행됩니다, 시뮬레이션 결과는 표 1에 언급된 표준의 특정 값 중 15kV 값과 비교될 예정입니다.

표 1. IEC 61000-4-2 테스트 레벨 및 ESD generator 파라미터

Air discharge ESD generator 모델

ESD generator는 일반적으로 일반적인 인체 방전을 재현하는 데 사용되며, 이를 통해 제품을 다음과 같이 테스트할 수 있습니다. 정확하고 효율적인 3D 모델링과 generator의 meshing은 해석 관점에서 매우 중요 합니다. Air discharge를 위한 ESD generator의 실제 설계는 복잡하기 때문에 metallic elements, resistors, capacitors, nonlinear arc로 구성된 선형 섹션으로 분리해야 합니다. 이에 상응하는 등가화된 3D 모델은 그림 2와 같이 CST Studio Suite에서 모델링하여 제공하고 있습니다.

Air discharge 의 경우, ESD generator에는 원형 방전 팁이 사용됩니다. 이 모양의 장점은 접촉 방전에 사용되는 원뿔형 팁에 비해 전하의 분산 강도가 높다는 것입니다.

그림 2. Air discharge을 위한 ESD generator 설계 및 캘리브레이션 설정

Rompe-Weizel 모델

Air discharge 의 물리적 테스트에서 대전된 팁은 Arc가 발생할 때까지 먼 거리에서 EUT 쪽으로 이동합니다. Arc는 ESD 발생기 팁과 DUT 사이의 틈에서 공기가 파괴되어 발생합니다. Rompe-Weizel 모델은 Arc의 전기적 거동을 모델링하는 데 사용되며 CST Studio Suite에서 Transient-co simulation을 사용하여 구현되었습니다. 본 모델은 시간 종속 Arc 저항을 시뮬레이션에 표시할 수 있으며 시뮬레이션 결과를 다양한 Arc 길이에 대한 물리적 테스트 데이터와 비교하기 위해 변수를 변경할 수 있습니다.

Rompe Weizel model은 아크 길이가 상승 시간 및 피크 전류에 미치는 영향을 설명하며, 아크 저항은 다음과 같이 계산됩니다.

여기서, R은 Arc 저항(Ω), d는 Arc 길이(m), a는 경험적 이온화 상수, i(ξ) 는 방전 전류(A)입니다.

Transient co-simulation

그림 3. CST Studio Suite Co-Simulation 셋업

CST Studio Suite는 시간 영역에서 Maxwell의 방정식과 아크 저항 방정식을 동시에 풀 수 있는 기능을 제공하여 주어진 형상, 충전 전압 및 아크 길이에 대한 전류 및 필드를 추정합니다.

그림 3에 표시된 transient co-simulation설정에서 Arc 저항은 3D 구조에 직접 연결된 SPICE 블록을 사용하여 모델링 됩니다. 이러한 저항은 ESD generator 3D 등가모델과 회로 시뮬레이터를 통해 연결됩니다. 회로 시뮬레이터는 SPICE 모델과 같은 비선형 요소를 모델링할 수 있습니다. SPICE 모델은 Rompe Weizel model을 구현한 것으로 Arc 길이 및 이온화 계수 파라미터를 변경하여 해석에 사용해 볼 수 있습니다. 매 time step마다 circuit 모델과 3D solver 간에 전압 및 전류 정보가 교환됩니다.

다양한 Arc 길이의 효과

전압과 속도가 동일하게 유지되더라도 Air-discharge 전류가 재현이 어렵다는 것은 잘 알려진 사실입니다. 이러한 이유는 Arc 길이가 다르기 때문입니다.

Paschen의 한계 값보다 긴 아크 길이는 매우 nonhomogeneous field에서 가능합니다. 그림 4는 5kV 충전 전압에 대한 Arc 길이가 ESD 전류 파형에 미치는 영향을 보여줍니다. Arc 길이 1.1mm는 Paschen 길이와 같으며, 이러한 방전 전류는 높은 습도와 느린 접근 속도에서 발생합니다. 이로 인해 짧은 아크 길이에 비해 느린 상승 시간(1.76ns)과 낮은 전류 피크 값(8.64A)이 발생합니다. 적당한 접근 속도는 Arc 길이 0.7mm에서 발생되며, 이 길이에서 상승 시간(0.72ns)은 IEC에 명시된 대로 Contact discharge ESD의 상승 시간과 어느 정도 유사합니다. 61000-4-2 표준과(0.7ns-1ns) 다소 유사합니다.

매우 짧은 Arc 길이는 높은 접근 속도와 건조한 공기에서 발생합니다. 그림 4에는 Arc길이 0.3mm의 전류 피크 값은 29.54A이고 상승 시간은 0.16ns입니다.

그림 4. 다양한 Arc 길이에 대한 ESD 방전 전류

팁 간격의 효과

물리적 ESD 테스트 중에 발생기 팁은 Arc가 발생할 때까지 다양한 속도로 EUT 쪽으로 이동합니다. 방전 시 Arc 길이는 DUT와 generator 팁 사이의 거리와 같습니다. 앞서 다양한 Arc 길이에 따른 효과를 확인한 그림 4는 언급한바와 같이 Arc 길이에 따른 효과 검증 을 할 수 있으며, Arc 길이가 팁과 test wall과의 간격과 동일하기 때문에 이 분석 결과를 통해 test wall과 팁의 간격을 설정해 볼 수 있습니다.

aR 변화의 효과

이상적으로는 경험적 이온화 상수인 aR 은 상수 입니다. 이 상수 값은 Rompe-Weizel 법칙에 의한 계산된 저항 값 비교했을 때 약간의 편차가 있을 수 있습니다. 정상 압력 하의 공기에서 aR의 문헌 값은 대부분 0.5x10-4 ~ 4x10-4 m2/V2 sec 범위입니다. 일부 전압 레벨에 대한 aR 의 기준 값은 “Computer Simulation of ESD from voluminous objects compared to transient fields of humans”[1]에서 참조할 수 있습니다.

CST Studio Suite를 사용하여 그림 5과 같이 aR 의 문헌 값 범위에 대한 parametric 분석을 진행해 보았습니다. 이는 ESD gen-erator 성능을 IEC 표준과 일치시키기 위해 적절한 aR 값을 선택해야 하는 경우 유효한 지표로 사용될 수 있습니다. 일반적으로 낮은 작동 전압의 경우 성능을 IEC 표준과 일치시키기 위해 더 높은 aR 값이 필요합니다.

그림 5. 다양한 aR값에 대한 ESD 방전 전류

다양한 전압 레벨에 대한 성능

설계된 ESD generator는 IEC ESD 표준을 준수해야 하므로 다음을 확인해야 합니다. 표준에 따라 다양한 공급 전압에 대한 성능을 검증해야 합니다. 설계된 ESD generator는 그림 6과 같이 다양한 공급 전압으로 시뮬레이션을 수행했으며 결과는 다음과 같습니다. 이는 ESD IEC 표준에 문서화된 수준과 잘 일치합니다.

그림 6. 다양한 전압에 대한 ESD 방전 전류

측정을 통한 검증

Air discharge 전류는 재현성이 낮기 때문에 시뮬레이션된 전류 파형과 측정값을 일치시키기가 어렵습니다. 따라서 일반적으로 ESD 전류에 대한 전류 도함수를 평가하는 것이 일반적입니다. 전류 미분은 ESD generator 전류 파형의 피크 전류 및 전류 상승 시간을 사용하여 계산됩니다. 그림 7은 Arc 길이가 감소함에 따라 전류 미분이 증가하는 것을 보여줍니다. 물리적 테스트 또는 시뮬레이션 중에 대역폭을 적절히 선택해야 빠른 과도 전류가 놓치지 않도록 대역폭을 적절히 선택해야 합니다.

SPICE Model을 이용한 유효성 검사

CST Studio Suite co-simulation에 Arc 저항을 모사하기 위해 사용되는 SPICE 모델의 정확성을 검증하기 위해 "Methodology for 3D full-wave simulation of electrostatic breakdown across an air gap"[2]의 내용을 기준으로 측정 결과와 시뮬레이션 결과를 비교해 보았습니다. 이때 Arc 모델 생성을 위한 SPICE 모델을 포함한 해석 결과와 [2]의 측정 결과를 피크 전류 및 전류 상승 시간을 통해 미분한 값으로 서로 비교해보면 그림 8과 같이 매우 잘 맞는 것을 확인 할 수 있습니다. 따라서 CST에서 제공하는 모델에 포함된 SPICE 모델을 이용하여 Arc 저항을 모사할 수 있으며, 이를 통한 Air discharge 해석에 활용해 볼 수 있습니다.

그림 7. 다양한 입력 전압에 대한 전류의 최대 시간 도함수 비교 그림 8. 5kV Air discharge을 위한 전류 파생 상품

ESD generator 검증

설계된 ESD generator를 추가로 검증하기 위해 "“Full-Wave Simulation of an Electrostatic Discharge Generator Discharging in Air-Discharge Mode into a Product "[3]을 참조했습니다. 참조에서 사용된 ESD generator 모델은 본 백서의 검증에 사용된 CST Studio Suite의 ESD generator 모델과 다르지만 유사한 전류 파생 결과가 나올 것으로 예상됩니다. 참조 모델의 피크 전류 파생 데이터는 그림 9과 같이 테스트 전압 5kV에 대해 본 백서에서 시뮬레이션한 CST Stu-dio Suite 모델과 잘 일치하는 것으로 나타났습니다. 세 번째 검증은 "Computer Simulation of ESD from voluminous objects compared to transient fields of humans "[4]의 모델을 참조하여 수행하였습니다. 10kV의 테스트 전압에 대해 시뮬레이션 된 피크 전류 및 전류 파생 데이터는 참조의 측정 값과 비교됩니다.

이러한 검증을 통해 그림 9 및 그림 10에 표시된 것처럼 CST Studio Suite에서 시뮬레이션 된 모델이 측정 결과와 거의 일치하는 것을 볼 수 있습니다.

그림 9. 10kV에 대한 시뮬레이션 피크 전류 그림 10. 10kV에 대한 피크 전류 미분 시뮬레이션

* 본 자료는 Dassault systems 의 ELECTROSTATIC DISCHARGE AIR 의 번역본입니다.

* 본 자료는 다쏘시스템 홈페이지 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

- 원본 : 다쏘시스템

관리자

2023.09.11

조회 516

|

|

|

[문서] CST Studio Suite을 활용한 전자파적합성 시뮬레이션

Dassault Systèmes

CST Studio Suite을 활용한 전자파적합성 시뮬레이션을 살펴보겠습니다. 본 글에서는 전자파 적합성이란 무엇인지, 시뮬레이션이 EMC에 어떤 도움이 되는지도 함께 보도록 하겠습니다.

전자파 적합성(EMC)이란 무엇인가요?

전자파 적합성(EMC)은 기기가 다른 기기와 간섭을 일으키지 않고 주변 환경에서 의도한 대로 작동하는 기능을 말합니다. 전자파 간섭을 제어하는 것은 모든 전자 장치 개발의 필수적인 부분입니다. 법에 따라 제품은 전자파 방출과 전기 및 전자 시스템의 민감성을 규제하는 국제 EMC 표준을 준수해야 판매할 수 있습니다. 성공적인 제품은 EMC와 크기, 비용 및 성능과 같은 경쟁 설계 요건 간의 균형을 유지해야 하며, 이는 엔지니어에게 큰 도전이 될 수 있습니다. 잠재적인 EMC 문제를 조기에 발견할수록 설계 프로세스에 대한 중단이 줄어듭니다. 초기 단계에서 EMC 적합성 설계를 포함하면 나중에 비용이 많이 드는 개발 반복을 피할 수 있습니다.

전자파 적합성(EMC) 규정은 디바이스가 다른 전자기기를 방해할 수 있는 전자기장을 방출해서는 안 되며, 주변 디바이스 및 낙뢰나 전자기 펄스 같은 환경 전자기 영향(E3)으로 인한 간섭을 견딜 수 있어야 한다는 것을 보장합니다.

시뮬레이션이 EMC에 어떤 도움이 되나요?

전자기 시뮬레이션을 통해 엔지니어는 회로 기판의 전류 흐름부터 공동 사이트 안테나 사이의 전계 전파에 이르기까지 디바이스의 모든 EMC 관련 측면을 자세히 살펴볼 수 있으며, 테스트 전에 잠재적인 문제를 식별하고 해결할 수 있습니다. 이를 통해 개발 시간과 비용을 절감할 수 있을 뿐만 아니라 규제 EMC 테스트에 실패할 위험도 줄일 수 있습니다. SIMULIA의 시뮬레이션 포트폴리오에는 빠르고 정확한 3D solver를 기반으로 하는 간섭 및 EMC 분석을 위한 다양한 전문 툴이 포함되어 있습니다.

EMC Software Applications:

EMC Rule Checking

EMC virtual testing

Co-site interference analysis

E3 - Electromagnetic Environmental Effects

Cable harness simulation

CST Studio Suite 기술을 사용하면 관련 EMC 범주 방출 및 민감성을 연구할 수 있습니다. 또한 매우 크고 복잡한 설정을 효율적으로 처리하거나 케이블과 같은 특정 문제에 특화된 solver 간의 하이브리드화를 사용하여 시스템 수준의 영향을 해석해 볼 수 있습니다.

휴대폰의 Crosstalsk 및 De-Sense 시뮬레이션

인터랙티브 인포그래픽에서는 휴대폰 설계에 영향을 미치는 전자파 적합성(EMC) 및 신호 무결성(SI) 문제를 짧은 동영상으로 소개합니다.

ESD 공기 방전 테스트 시뮬레이션

공기 방전 방법에서는 테스트 제너레이터의 충전된 전극을 DUT에 가깝게 가져와 스파크에 의해 방전이 장치에 작동됩니다. 이 백서에서는 정전기 방전(ESD) 발생기 테스트 설정을 SIMULIA CST Studio Suite를 사용하여 모델링하고 IEC 표준 IEC 61000-4-2에 지정된 공기 방전에 대한 다양한 테스트 레벨에 대해 시뮬레이션을 수행합니다.

ESD 테스트 시뮬레이션-Contact Discharge방법

정전기 방전 테스트를 위한 접촉 방전 방법에서는 테스트 발생기의 전극이 테스트 대상 장비(EUT)의 전도성 부분과 직접 접촉하고 발생기 내의 방전 스위치에 의해 작동되는 방전이 유지됩니다. IEC 61000-4-2는 ESD 발생기에 의해 주입된 파형을 보정하는 절차를 설명합니다. 파형 특성은 이상적인 발전기 파형 특성과 비교됩니다.

Bulk Current Injection

전자 기기의 내성을 테스트하는 비침습적 방법인 벌크 전류 주입(BCI) 기법에 대해 자세히 알아보세요.

본 자료는 다쏘시스템 홈페이지의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템 홈페이지

관리자

2023.09.07

조회 389

|

|

|

[문서] 낙뢰 및 EMP로부터 건물 보호: 전자기 시뮬레이션이 도움이 될 수 있습니다.

Wi-Fi가 한 시간만 끊겨도 우리가 인터넷 연결에 얼마나 의존하고 있는지 깨닫게 됩니다. 현대 생활의 많은 부분이 디지털 연결과 인프라에 의존하고 있기 때문에 데이터 센터와 같이 이러한 연결을 제공하고 데이터를 저장하는 건물이 의도적이든 의도적이지 않든 전자기(EM) 이벤트로부터 보호되는 것이 매우 중요해졌습니다.

낙뢰

낙뢰는 극적이고 아름다울 수 있지만, 폭풍우가 치는 동안 골프 코스로 나가지 않는 것이 좋다는 것은 우리 모두는 잘 알고 있습니다. 그렇다면 낙뢰란 무엇이며 디지털 시스템에 어떤 영향을 미칠 수 있을까요?

낙뢰는 폭풍 구름 내의 물이나 얼음 입자에 전하가 쌓이고 전기장이 충분히 높아져 공기가 전자와 양이온으로 분해될 때 발생합니다[1]. 이 이온화된 공기 영역에서는 계단 모양의 일련의 전하가 지구를 향해 내려가는 '계단선도'가 발생합니다. 계단형 리더가 지면에 가까워지면 반대 전하를 띤 '스트리머’가 위로 올라와 이를 만나고 구름과 지면 사이에 전도 채널이 형성됩니다. 이렇게 하면 전류 펄스가 흐르면서 구름이 방전되는 현상이 낙뢰입니다. 이 '리턴 스트로크'는 수만 또는 수십만 암페어의 최고 수준에 도달할 수 있으며 매우 뜨겁기 때문에(최대 30,000oC - 태양보다 5배 더 뜨겁습니다!) 주변 공기가 빠르게 팽창하여 우리가 천둥소리로 듣는 충격파를 만들어 냅니다.

특히 건물이 높고 금속이 좋은 전기 전도체이기 때문에 구조물의 금속으로 인해 저항이 낮은 채널을 제공하는 경우 건물이 낙뢰에 선호되는 경로를 제공할 수 있습니다. 그러면 건물은 낙뢰 채널의 일부가 되어 강렬한 귀환낙뢰 전류에 직접 노출됩니다. 낙뢰 전류 펄스에는 상당한 가열을 일으킬 수있는 충분한 에너지가 포함되어있어 잠재적으로 구조적 손상을 초래할 수 있습니다. 전류와 관련된 고강도 자기장[2]은 케이블 및 전기/전자 시스템에 유해한 전류와 전압을 유도하여 IC 또는 저장 장치와 같은 민감한 전자 부품을 파괴할 수 있습니다. 자기장이 여전히 중요한 인프라를 손상시키기에 충분한 수준에 있을 수 있기 때문에 근처의 간접 낙뢰도 우려됩니다.

Electromagnetic Pulse (EMP)

비핵 EMP는 전기 및 전자 시스템에 손상을 입힐 수 있다는 점에서 많은 액션 영화의 줄거리에서 상상되어 왔지만, EMP가 건물이나 도시의 디지털 인프라를 전멸시킬 수 있다는 생각은 얼마나 정확한 것일까요? EMP는 자연적으로 발생하거나 인간 활동의 결과로 발생할 수 있는 실제 현상입니다. 자연 발생의 예로는 태양 코로나에서 플라즈마가 폭발하고 그 안에 내재된 자기장이 방출되어 발생하는 태양 EMP가 있습니다. 인공 EMP의 예로는 입자가 지구 대기 및 자기장과 상호 작용하여 핵폭발(NEMP)의 결과로 발생하는 펄스를 들 수 있습니다.

EMP는 미터당 수만 볼트의 피크 전기장 수준의 고강도 전자기파를 생성합니다. 이러한 전자파가 건물에 도달하면 창문, 문 주변의 이음새, 통풍구, 파이프와 같은 구멍을 통해 케이블을 통해 건물 내부로 들어올 수 있습니다. 건물 내부에 도달하면 EMP로 생성된 자기장이 전자 시스템에 결합하여 전압과 전류를 유도하여 민감한 전자 장치를 심각하게 손상시키거나 태워버리고 저장된 데이터를 파괴할 수 있습니다.

디지털 인프라 보호

낙뢰 보호에는 부분적으로 민감한 시스템에서 전류를 전환하는 것이 포함됩니다. 예를 들어 에어 터미널이나 피뢰침은 제어된 위치에서 번개를 수집하고 지상으로 안전하게 전도하는 차단 지점 역할을 할 수 있습니다.

차폐는 저주파 자기장이 건축 자재를 통해 확산되는 것을 방지하는 데 사용되며 케이블에도 적용될 수 있습니다. EMP 보호에는 일반적으로 결합/전달을 줄이기 위해 개구부를 EMP와 관련된 파장보다 작게 유지하고, 차폐를 적용하여 보호 구역(예: 데이터 서버 홀)을 만드는 것이 포함됩니다. 전도성 개스킷을 이음새에 설치하여 개구부를 효과적으로 제거하고, 전도성 코팅을 창문에 적용하여 유리 재질을 통한 전계 투과를 감쇠시킬 수 있습니다.

필터링 및 과도 보호 장치를 사용하여 커넥터 인터페이스의 전압과 전류를 감쇠하거나 클램핑할 수 있습니다. 이러한 장치는 케이블 시스템이 건물에 들어오는 진입 지점(POE)에 적용할 수 있습니다. 유틸리티 파이프에 설치된 금속 메시 구조는 전자파를 필터링하여 전자파가 건물 내부로 유입되는 것을 방지합니다.

시뮬레이션이 도움이 되는 방법

물리 기반 시뮬레이션을 사용하면 디지털 인프라 설계의 낙뢰/EMP 취약성을 새 건물을 건설하기 전이나 기존 건물을 업그레이드하기 전에 평가하여 전자기 효과를 강화할 수 있습니다. 서로 다른 보호 체계를 분석하여 효율성을 평가할 수 있습니다. Parametric sweeps 및 optimizers를 사용하여 설계 트레이드오프를 연구하고 과도한 엔지니어링을 방지함으로써 건축 자재 비용을 절감합니다.

다분야 물리 기반 시뮬레이션을 사용하여 전자기 보호를 위해 구현된 설계 기능이 구조적 무결성이나 냉각 시스템 성능을 손상시키지 않거나 그 반대의 경우도 마찬가지임을 보장할 수 있습니다. 예를 들어 냉각 시스템의 일부로 건물에 배치된 금속 배관 또는 덕트는 잠재적으로 전자기장과 전류를 건물로 운반하는 도관 역할을 할 수 있으며 전자기 공명 효과로 인해 전자기장을 강화하고 손상을 악화시킬 수도 있습니다. .

Virtual Twin을 사용하는 오늘날의 최신 시뮬레이션 기술은 모든 엔지니어에게 전체 시스템에 대한 완전한 이해를 제공함으로써 혁신을 위한 완전히 새로운 길을 열어줍니다. CST Studio Suite 기술을 사용한 시뮬레이션을 통해 필드 및 결합 경로를 시각화하여 건물의 전자기 성능에 대한 뛰어난 통찰력을 제공하여 최적의 설계 및 보호로 이어집니다. 3DEXPERIENCE 플랫폼을 통해 SIMULIA EM 시뮬레이션 기술에 액세스함으로써 모든 이해 관계자는 설계에서 시뮬레이션, 제조에 이르는 연속성을 위해 최신 데이터로 작업합니다.

References

[1] https://www.weather.gov/jetstream/lightning

[2] Ampère’s law

본 자료는 다쏘시스템 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템 블로그

관리자

2023.07.06

조회 444

|

|

|

[문서] CST Studio Suite을 활용한 EMP 방호 시설 해석 사례 소개

CST Studio Suite을 활용한 EMP 방호 시설 해석 사례 소개합니다.

전자기 펄스는 강력한 전자 폭풍의 원인이 되는 핵폭발, 전자폭탄의 폭발 그리고 낙뢰와 같은 자연현상에 의해서 그 폭파 범위 내에 있는 모든 전자제품이 영향을 받아 정상적인 동작을 할 수 없게 만드는 역할을 합니다. 이러한 전자기 펄스는 크게 3가지 종류로 구분이 되는데, 앞서 설명한 대로 핵폭발로 인해 발생되는 핵 전자기 펄스 (Nuclear EMP), 비핵 전자기 펄스 (Non-Nuclear EMP) 그리고 자연현상에 의해 발생되는 전자기 펄스 (Lightning EMP)로 분류될 수 있습니다.

전자폭탄은 전자기 펄스를 무기화 한 것인데요. 공중에서 폭파될 경우 주변의 전자기기에 막대한 영향을 미친다고 알려져 있습니다. 2003년 3월 26일 이라크전에서 미연합군이 고출력 극 초단파 (High-Power Microwave)를 사용하였는데, 이것은 1초 내에 20억 와트 전력을 방사하여, 1km 내부에 모든 전자기기들을 무력화 시킨 바 있습니다. 이러한 전자기 펄스의 영향 때문에, 각 나라에서는 전자기 펄스의 방호에 많은 관심과 투자가 이루어지고 있다고 합니다.

이러한 강력한 영향력을 가지고 있는 전자기 펄스에 대해서 “내구성을 가진다”를 무엇을 가지고 평가를 할까요? 밀리터리 스탠다드 테스트 (MIL-STD)로 불리는 미 국방성의 시험 표준이 바로 그것입니다. 하위 항목인 MIL-STD-464는 시스템의 전자기 환경 영향 요구 사항입니다. 여기에서 전자기 환경이라는 것은 자연적 발생원 (낙뢰, 정전하 방전, 은하 잡음 등)과 인공 발생원 (전자기기, RF 시스템, 고 전력, 극 초단파 등)과 같은 다양한 전자기 에너지를 의미합니다. MIL-STD-464에서 규정하고 있는 전기장을 사용하여 방호를 위한 규격의 만족 여부를 판단하는데, 시뮬레이션을 활용한 분석에서는 방호를 위한 시스템 (건물, 전자기기 등)의 외부로부터 평면파를 인가하여 시스템 내부의 전자기 수준을 확인하는 것으로 내구성을 예측해 볼 수 있습니다. 아래 내용은 건물의 기본 구조, 건물에 도어가 있는 구조, 건물에 케이블이 있는 구조, 3가지의 해석 모델을 가지고 건물 내부의 전자기 수준을 분석하는 내용이 소개됩니다.

CST Studio Suite을 활용한 EMP 방호 시설 해석 사례 소개

다쏘시스템코리아

전자기 펄스 방호 해석

기본 구조

전자기 펄스 방호 해석을 위한 건물은 그림 2와 같이 구성됩니다. 건물의 외형은 3.3 x 2.4x3.15 m3이며, 유전율이 4.5인 콘크리트 구조물입니다. 건물의 내부는 철근으로 구성되어 있고, 철근의 내부는 그림 2(c)와 같이 차폐 구조가 형성되어 있습니다. 도전율은 3.56 x 10e7이고, 두께는 0.001m로 얇은 형태입니다. CST Studio Suite에서 차폐 구조를 “thin panel”로 설정을 하면, 다층 구조 형상을 하나의 얇은 2차원 면에 모두 표현할 수 있는 장점이 있습니다. 층마다 물성과 두께를 줄 수 있을 뿐만 아니라, 주파수에 따른 표피 효과도 확인할 수 있고, 다층 구성에 비해 해석 시간도 빠르게 가져갈 수 있는 장점이 있습니다. 해석을 위해 설계된 건물의 경계면은 하단을 제외하고 방사 조건으로 설정을 하였고, 건물의 하단은 접지 설정을 위해 도체로 설정하였습니다.

(a) 건물 외형 (콘크리트) (b) 콘크리트 보강용 철근 (c) 차폐 구조

그림 2. 전자기 펄스 해석을 위한 건물 구조

설계된 건물에 MIL-STD-464에서 규정하고 있는 전기장을 인가해야 하는데, 방법은 평면파를이용하면 됩니다.

그림 3. 평면파와 전기장

그림 3은 건물의 상단 부분에 평면파를 인가하여 전자기 펄스가 인가되는 상황을 구현한 것입니다. 해석의 목적은 건물에 적용된 전자기 펄스 방호 구조물 (철근, 차폐 구조)의 전자기장 차폐 효과를 보기 위함입니다. 건물 내부의 중앙 부분에 전기 프로브 (그림2(d))를 통해서, 방호 구조물의 차폐 효과를 비교해볼 수 있습니다. 다음의 3가지 타입에 대한 차폐 효과를 비교해보려고 합니다.

콘크리트 구조 (Concrete)

콘크리트 + 철근 구조 (Concrete + Rebar)

콘크리트 + 철근 + 차폐 구조 (Concrete + Rebar + Shielding wall)

그림 4. 전기장 값 비교 (시간 영역)

그림 4의 결과를 확인해 보면, 방호를 위한 구조물이 추가될수록 건물 내부에서의 전기장의 값이 낮아지는 것을 확인해볼 수 있습니다. 이는 외부로부터 인가되는 전기장이 차폐가 되면서 건물 내부에는 그 영향이 미치지 않는 것을 확인할 수 있는 해석입니다.

그림 5. 전기장 값 비교 (주파수 영역)

그림 5는 주파수에 따른 전기장을 나타내고 있습니다. 앞선 결과와 마찬가지로 차폐 구조물의 효과를 확인해 볼 수 있는데요. 콘크리트 + 철근 + 차폐 구조가 있을 경우 (파란색)에 주파수에 따른 전기장 수준이 낮은 것을 확인할 수 있습니다. 각 타입에 대해서 2차원 전기장을 비교해서 좀 더 자세하게 살펴볼 수 있습니다.

(a) 콘크리트 (b) 콘크리트 + 철근 (c) 콘크리트 + 철근 + 차폐 구조

그림 6. 2차원 전기장 분포 (주파수 영역)

그림 6에서는 전자기 펄스 방호를 위한 구조물의 차폐 효과를 조금 더 확실하게 살펴볼 수 있습니다. 전자장의 스케일을 동일하게 설정한 상태에서, 붉은 색은 전기장의 세기가 크다는 것을 표현해주고 있고, 푸른색은 전기장의 세기가 작다는 것을 표현해주고 있습니다. 앞선 그림 4, 5의 2D 결과와 마찬가지로 방호를 위한 구조물이 차폐를 위한 역할을 하고 있다는 것을 확인할 수 있습니다.

기본 구조 + 도어

(a) 콘크리트+철근 (b) 차폐 구조 (c) 도어

그림 7. 도어가 있는 방호 건물의 전자기 펄스 시뮬레이션

그림 7은 도어가 있는 방호 건물의 전자기 펄스 시뮬레이션을 나타내고 있습니다. 여기에서는 도어의 겹치는 면적을 2가지로 설정한 후 내부 프로브에서의 전기장 값을 확인하는 것이 목표입니다.

(a) 원본 모델 (b) 컴팩트 Seam 모델

그림 8. Seam 정의

도어의 경우에는 부피가 없는 2차원 면으로 형성하였고, “Seam” 형태로 구성하였습니다.

“Seam”은 Shape > Face and Apertures > Slot을 선택하고 type에서 “Seam”을 선택하면 설정할 수 있습니다. “Seam” 설정에서 도어가 겹치는 면적을 설정할 수 있습니다. 이 면적의 저의는 그림 8을 보면 확인할 수 있습니다. 두 개의 평면이 서로 겹쳐지는 면적이 발생하는 상황에서 겹치는 면적의 크기를 기입할 수 있습니다. 그림 8(b)는 컴팩트 Seam 모델을 나타낸 것으로 실제 CST MWS 상에서는 그림 8(b)와 같은 형태로 표현됩니다. 앞의 기본 구조에 대한 시뮬레이션과 동일하게 건물의 상단에 평면파를 인가하였습니다.

그림 9. 면적 차이에 따른 전기장 값 비교 (시간 영역)

그림 10. 면적 차이에 따른 전기장 값 비교 (주파수 영역)

그림 10은 면적 차이에 따른 전기장 값 (주파수 영역)을 비교한 결과입니다. 특정 주파수 (130MHz)에서의 전기장 최대값은 차이가 있지만 전체적으로 최대값이 나타나는 주파수와 그 크기는 비슷한 결과를 보이고 있습니다.

그림 11. 면적 차이에 의한 2차원 전기장 값 비교

그림 11은 2차원 전기장을 비교한 결과입니다. 30ns에서 건물 내부의 전기장 분포를 나타낸 결과입니다. 붉은색은 전기장 값이 높다는 것을 의미하고 파란색은 전기장 값이 낮음을 표현하고 있습니다. 겹치는 면적이 큰 경우 (100mm)의 건물 내부가 전체적으로 파란색을 나타내고 있고 또한 차폐 성능이 우수하여 건물 내부의 전기장 값이 낮게 분포하고 있음을 나타내고 있습니다.

케이블

마지막 전자기 펄스 시뮬레이션은 기본 구조 + 케이블 구조입니다. 전자기 펄스 건물 주변에는 케이블이 존재할 경우가 있는데, 전자기 펄스가 케이블에 인가가 되어 건물 내부에서 방사가 될 수 있습니다. CST Cable Studio (CST CS)를 활용하여 전자기 펄스 건물에 케이블을 설계하여 삽입하고 CST Design Studio (CST DES)를 활용하여 TVS 다이오드 효과, 접지에 의한 전기장 변화를 살펴볼 예정입니다.

(a) 해석 모델 (b) 해석 케이블 (케이블 1, 케이블 2)

그림 12. 케이블 해석 모델

그림 12는 케이블 해석 모델을 나타내고 있습니다. 그림 12(a)에 보면, 케이블은 건물의 하단에 위치합니다. 해석을 위한 케이블은 두 부분으로 나뉩니다.

케이블 1: 외부 > 건물 벽

케이블 2: 건물 벽 > 내부

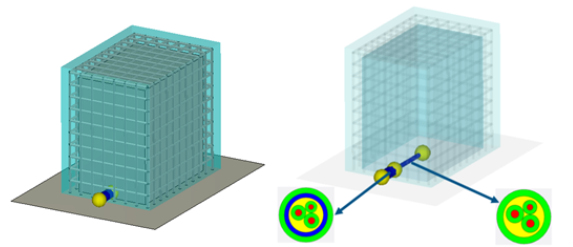

그림 13. 케이블 1

케이블 1은 그림 13과 같이 구조 내부에 금속 선들이 있어서, 외부 전자기파가 쉽게 침투하지 못하는 구조입니다. 케이블 2는 금속선이 없어 케이블로 침투된 전류에 의해 방사가 될 수 있는 케이블 구조입니다. CST CS는 케이블의 단면을 등가화하여 케이블의 신호 무결성 (Signal Integrity), 전자기파 적합성 (Electro-magnetic Compatibility) 해석을 할 수 있는 제품입니다. CST CS에서는 단선, 트위스트 케이블, 리본 케이블, 동축 케이블 형태에 대해서 각각을 물성 설정, 내부 구성 등을 설정할 수 있습니다. 앞선 시뮬레이션과 동일하게 건물의 상단에 MIL-STD-464에 규정되어 있는 전기장이 인가되었습니다.

(a) 개방 (b) 개방 + TVS 다이오드 (c) 단락

그림 14. 3가지 케이블 해석

케이블의 영향도 분석을 위해 3가지 상황에 대해서 시뮬레이션 분석이 진행됩니다.

개방

개방 + TVS 다이오드

단락

그림 14에서 보듯이, 개방의 경우는 케이블 1의 다중 가닥 금속선 부분에 10k Ohm을 연결하여, 차폐 효과가 없는 상태(개방)를 구현하였고, 개방 + TVS 다이오드는 앞선 개방 조건에서 정전기 방지 역할을 하는 다이오드를 연결한 경우입니다. 단락의 경우는 케이블 1의 다중 가닥 금속선 부분을 접지한 경우입니다.

그림 15. 시간 영역에서의 전기장 비교

그림 16. 주파수 영역에서의 전기장 비교

그림 15와 16은 각각 시간과 주파수 영역에 대한 전기장 수준을 시뮬레이션 한 결과입니다. 앞의 3가지 시뮬레이션 결과에 대해서 전자기 펄스 건물 내부의 전기장 값을 비교한 결과입니다. 단락을 제외하고 나머지 상황에서의 전기장 수준은 상당히 높음을 알 수 있습니다. TVS 다이오드가 케이블 2 끝에 연결이 되어 있어, 케이블 2에서 방사된 전자기장을 막아주지 못하고 있어 건물 내부의 프로브에 높은 값이 나타나게 됩니다. 단락의 경우에 전기장 값은 케이블 1의 금속 선과그라운드와의 접지와 인해, 외부 평면파가 케이블 2로 전달되지 않고 접지로 빠져나가게 됩니다.

(a) 개방 (b) 개방 + TVS 다이오드 (c) 단락

그림 17. 2차원 전기장 분포

그림 17은 2차원 전기장 분포 결과입니다. 결과에서 보듯이 단락일 때, 건물 내부의 전기장이 유기되지 않아 내부 케이블 2 주변 (검은색 선)의 전기장 값이 낮은 것을 확인할 수 있습니다.

그림 18. TVS 다이오드 연결 위치

그림 18은 TVS 다이오드의 연결 위치를 나타낸 것입니다. 1번 위치는 케이블 1의 끝에 다이오드가 연결된 것을 의미하고, 2번은 케이블 2의 끝에 다이오드가 연결된 상태입니다. TVS 다이오드 위치에 따라 내부 전기장의 값이 다르게 분포하는데 이를 분석하기 위해서 1번과 2번 위치에서의 전기장 값을 비교해 보았습니다.

그림 19. TVS 다이오드 위치에 따른 전기장 비교

그림 19는 TVS 연결 위치에 따른 내부의 전기장 값을 나타낸 것입니다. 같은 개방 조건에서도 TVS 다이오드의 연결 위치에 따라 내부로 침투하는 전기장을 저감하는 효과를 가져올 수 있습니다.

맺음말

지금까지 방호 건물에 대한 시뮬레이션 과정과 결과에 대해서 분석해 보았습니다. MIL-STD-464에서 규정하고 있는 전기장을 인가하여 건물에 대해서 전자기 펄스 방호 능력을 시뮬레이션을 통해 확인해 보았습니다. 건물 내부에 전기자 프로브 하나를 두어 시뮬레이션 검증을 하였으나, 엔지니어는 규정이 정하는 방식에 맞도록 시뮬레이션을 진행해야 할 것입니다. 케이블 해석에 대해서도 종류와 길이, 개수 등 정확한 정의를 내리고 나서 시뮬레이션이 진행되어야 정확한 결과와 검증이 이루어질 것입니다.

현재는 미 국방성 규격에 따라 국방 시설에 대해서 시험 평가를 수행하고 있으나, 민간시설에서 운용하고 있는 전자기기와 제품에 대한 전자기 펄스 규격 제정은 미미한 상황이어서 국제 규격 제정이 필요한 상태입니다. 이러한 규격화 작업에서 시뮬레이션 검증은 상당히 중요해 보입니다. 제품 테스트 적용 전에 시뮬레이션으로 사전 검증을 해봄으로써, 다양한 상황에 대해서 방호 성능을 예측해 볼 수 있기 때문입니다.

본 자료는 다쏘시스템 코리아 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템코리아 블로그

관리자

2021.10.22

조회 1199

|

|

|

[문서] CST Studio Suite을 이용한 EMI/EMC 해석

다쏘시스템사의 소프트웨어인 SIMULIA의 CST Studio Suite을 이용한 EMI/EMC 해석 사례를 살펴보고자 합니다.

전자기 적합성(EMC)을 왜 CST Studio Suite을 이용하여 분석해야 하는지, 그리고 어떠한 해석들을 진행할 수 있는지 소개 드리겠습니다.

"CST Studio Suite을 이용한 EMI/EMC 해석"

다쏘시스템코리아

EMI/EMC란?

우리는 일상생활 속에서 전자제품들이 저절로 켜지거나 꺼지는 상황들, 차량에서 핸드폰을 이용하여 통화할 때 스피커에서 “지지직-“거리는 소리가 들리는 상황 등을 경험하곤 합니다. 이런 일들이 발생하는 이유는 전기/전자 기기를 사용할 때 전파되는 원치 않는 전자기력 에너지(보통 노이즈라 칭함)가 다른 장비에 영향을 줄 때 발생하게 됩니다. 이러한 영향은 제품의 신뢰성, 크게는 인명 사고로도 이어지고 있습니다. 경고 없이 갑자기 작동되는 에어백 문제로 약 백 만대의 차량을 리콜했던 사례가 있었으며, 핸드폰 사용으로 인해 수술용 의료기기가 오작동하여 환자가 사망하는 사고도 있었습니다. 이렇게 전자기의 노이즈는 우리의 생활에 크고 작은 사고를 만들어 낼 수 있는 위험 요소라 볼 수 있습니다.

그림 1. 전기, 전자 제품이 발생시키는 노이즈 성분

위와 같은 전자기 장해로 인한 사건 사고를 줄이기 위해서는 전기, 전자 제품들을 개발하는 과정에서 기기에서 방출되는 전자기 노이즈 성분을 줄이고, 반대로 전자기 노이즈의 영향을 받았을 때 어느 정도 내성을 갖추도록 설계가 되어야 합니다. 이것을 확인하는 과정이 전자기 적합성(Electro Magnetic Compatibility – EMC) 시험입니다. 전자기 적합성(EMC) 시험은 전기, 전자 제품이 어떤 분야에서 사용되느냐에 따라 다양한 규격(Standard)을 가지고 있습니다. 이 규격에는 전자기 적합성(EMC) 시험 환경 및 방법, 신호원, 노이즈의 허용치와 같은 정보들이 정의되어 있습니다. 따라서 제품에 맞는 규격에 따라 시험을 수행한 뒤, 전자기 노이즈가 허용치보다 높은 경우 허용치보다 낮은 노이즈를 갖기 위한 EMC 대책을 강구해야 합니다.전자기 적합성(EMC) 시험은 크게 두 가지로 나누어 볼 수 있습니다. 하나는 전기, 전자 기기가 외부로 얼마나 전자기 노이즈를 방출하는지 확인하는 전자기 장해(Electro Magnetic Interference – EMI), 다른 하나는 전기, 전자 기기가 외부에서 전자기 노이즈를 받았을 경우 어느 정도의 내성을 갖추었는지를 확인하는 전자기 민감성(Electro Magnetic Susceptibility 0 EMS) 입니다. 또한, 이는 각각 방사성 전자기 노이즈에 의한 부분과 (Radiated Emission – RE / Radiated susceptibility – RS) 전도성 전자기 노이즈에 의한 부분 (Conducted Emission – CE / Conducted Susceptibility – CS)으로 나누어 볼 수 있습니다.

그림 2. EMC 종류와 구분

전자기 적합성(EMC)은 노이즈가 어떠한 경로를 통해 방출되고, 유입되는지에 따라 다른 구분을 갖게 되고, 이러한 구분 내에서도 다양한 규격과 다양한 시험들이 존재합니다.

본문에서는 전자기 적합성(EMC)을 CST Studio Suite을 이용하여 왜 시뮬레이션을 하여 분석해야 하는지, 그리고 어떠한 해석들을 진행할 수 있는지 소개 드리도록 하겠습니다.

EMI/EMC 분야에서 시뮬레이션의 필요성과 CST Studio Suite의 장점

“눈으로 보는 전자기장”

전자기(Electromagnetic) 현상들은 눈으로 볼 수도 느낄 수도 없습니다. 또한 직관적으로 현상이 나타나지 않기 때문에 전자기 적합성(EMC) 문제가 발생할 경우 어느 부분에서, 어떤 문제에 의해 발생하는지를 분석하는 것에 어려움이 있습니다.

하지만 전자기장 해석 소프트웨어들은 시각화된 전자기 필드 결과들을 통해 발생한 노이즈 성분들이 어떠한 경로를 통해 영향을 주고, 어떠한 부분에 크게 영향을 주는지에 대한 사항들을 파악하는데 도움을 줍니다.

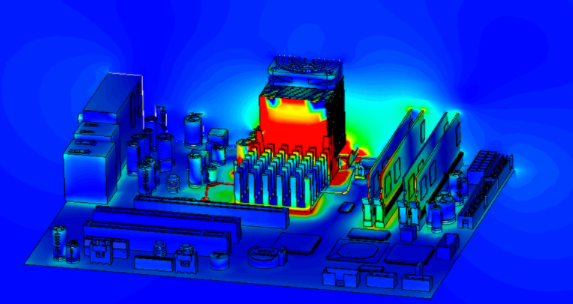

그림 3. 시뮬레이션을 통해 본 Heat Sink에 의해 발생하는 전자기 장해(EMI)

“EMC 대책에 대한 분석”

그리고 전자기 적합성(EMC) 문제가 발생할 경우 EMC 엔지니어는 대책을 세우게 되는데, 이러한 대책에는 PCB layout 변경, 대책 소자 사용, 차폐(Shielding), 그라운드 접지 등 다양한 방법들이 존재합니다.

시뮬레이션에서는 이러한 대책들에 대한 쉬운 정의가 가능하고, 대책 전후의 결과를 빠르게 비교해 볼 수 있습니다.

그림 3은 대책 전 Multimedia 장비에 외부로부터 방사된 노이즈 성분이 유기되어 동작에 영향을 받았는데, Amplifier holder에 5pF의 커패시터 부착 후 방사 노이즈에 의한 영향이 줄어든 것을 확인했던 사례입니다.

그림 4. Multimedia 시스템의 방사 민감성 (RS) 결과

사례들을 통해 볼 수 있듯이 시각화된 결과 도출과 대책을 빠르게 적용하여 전후의 결과를 확인할 수 있다는 점이 전자기 적합성(EMC)를 분석하는 엔지니어와 전자기를 전공하지 않은 분들에게 이를 전달할 때 많은 도움이 되는 것을 확인할 수 있었습니다. 그렇다면 이러한 전자기 적합성(EMC) 분석을 진행할 때 CST Studio Suite을 이용해야 하는 이유는 무엇일까요? 이는 크게 네 가지 사항으로 나눠서 볼 수 있습니다.

7개의 Product, 20개가 넘는 Solver를 이용한 다양한 분야의 분석 가능

CAD import 및 EDA import 기능

강력한 메쉬 기법을 이용한 복잡한 구조 해석 가능

가속기를 이용한 빠른 해석 가능

전자기 적합성(EMC) 문제는 다양한 구분과 규격을 갖고 있기 때문에 그에 맞춰 분석을 하기 위해서는 여러 Product과 Solver들을 사용해야 하는 경우가 있습니다. CST Studio Suite은 하나의 패키지 안에서 전자기 적합성(EMC) 분석에 필요한 다양한 Product와 Solver 제공을 통해 최적화된 해석 환경을 갖추어 분석을 진행할 수 있습니다.

그림 5. EMC 분석을 위해 사용되는 CST Studio Suite의 Products

전자기 적합성(EMC) 분석을 진행하기 위해서는 PCB, 기구, 케이블, 물성 등 다양한 데이터들을 불러와야 하는 경우가 발생합니다. 이러한 경우 CAD import와 EDA import 기능, 그리고 다양하게 지원되는 물성 정보들을 통해 사실적인 환경 구현을 통한 정확한 분석을 진행할 수 있습니다.

그림 6. CST Studio Suite에서 지원하는 CAD, EDA, 물성 정보

다양한 모델 데이터들을 불러오게 되면 복잡도와 분석 영역의 크기에 따라 해석이 어려워질 수 있습니다. 특히 복잡한 PCB 구조와 기구 데이터들을 함께 두고 해석을 진행하는 경우에는 해석을 위한 메쉬를 나누는 과정에서 큰 어려움을 겪게 됩니다. CST Microwave Studio에서 제공하는 메쉬 기법인 PBA(Perfect Boundary Approximation), TST(Thin Sheet Technique)은 하나의 메쉬 셀 안에 두 가지 혹은 세 가지(유전체 2, 도체 1) 물성이 들어오더라도 에러 없이 해석을 진행할 수 있습니다. 이러한 강력한 메쉬 기법들은 PCB, 기구, 케이블, 플랫폼 구조가 함께 있는 상태에서의 Full 3D EM Simulation을 가능하게 하며 이러한 분석들은 직관적이고 실질적인 결과로 활용될 수 있습니다.

그림 7. 차량용 배터리의 Open/Short 조건에 따른 Radiated Field 분석

마지막으로 GPU(Graphic Processing Unit)을 이용한 해석의 가속이 가능합니다. CST Studio Suite에서 해석의 가속으로 사용 가능한 GPU 모델을 가지고 해석을 진행하게 되면 기존의 해석보다 수십 배(최신 GPU의 경우) 빠른 해석을 경험할 수 있습니다.

전자기 적합성(EMC) 분석에서 CST Studio Suite은 위에서 설명했던 장점들을 이용하여 Transportation & Mobility, Aero & Defense, High Tech 등 다양한 분야, 그리고 다양한 회사들에서 분석에 사용되고 있는 전자기장 소프트웨어입니다. 그렇다면 CST Studio Suite을 이용하여 어떠한 해석들을 진행할 수 있는지에 대해 살펴보도록 하겠습니다.

Electro Magnetic Interference(EMI) 분석

전자기 장해(EMI)는 앞서 소개 드렸던 거 같이 전자기기가 얼마만큼의 전도성, 혹은 방사성 노이즈를 방출하는지를 확인해 보는 분석입니다. 해당 분석 중 방사성 노이즈에 의한 전자기 장해(EMI) 측정은 보통 아래와 같은 시험 규격을 갖게 됩니다. 피실험 기기인 EUT(Equipment Under Test)를 Table 위에 올려놓고 동작을 시킵니다. 그때 고정되어 있는 3m 혹은 10m 거리에 떨어진 Antenna를 통해 얼마만큼의 노이즈가 방사되는지를 측정하게 되고, Table을 회전시켜 EUT의 모든 방위에서의 방사성 노이즈를 측정합니다.

그림 8. 방사성 노이즈 측정 Test Set

방사성 노이즈 전자기 장해(EMI) 시뮬레이션의 경우 실제 측정 시험 환경을 모두 모사하여 해석을 진행해 볼 수 있습니다. 하지만 이러한 경우 무반사실과 시험에 필요한 기구들을 모두 모사하여 해석을 진행해야 하기 때문에 많은 하드웨어 리소스가 필요하고 오랜 해석 시간이 요구됩니다.

그림 9. Continental에서 진행한 측정 Test Set을 모사한 방사성 노이즈 측정

따라서 그림 10과 같이 EUT만 해석상에 불러온 상태에서 3m 혹은 10m 밖에 모든 방위에 걸쳐 E-field 프로브를 설정한 다음, 각 프로브에서 얻어지는 E-field 값을 모두 얻어낼 수 있습니다. 또한 이렇게 얻어진 여러 E-field들 중 각 주파수 별로 가장 높은 E-field 값으로만 추출하여 각 주파수 별 Worst case에 대한 EMI 스펙트럼 결과를 얻어낼 수 있습니다.

그림 10. EUT를 중심으로 3m 밖 Spherical 영역에 프로브 설정 후 주파수 별 Worst case 추출

이렇게 두 가지 방법을 통한 분석을 진행할 수 있기 때문에 사용자의 하드웨어 및 원하는 결과에 맞춰 선택적으로 Workflow를 가져갈 수 있습니다.

전도성 노이즈에 의한 전자기 장해(EMI)에 대해서도 CST Studio Suite을 이용하여 분석을 진행해볼 수 있습니다. 그림 11은 Motor control system에서의 3상 제어를 위한 H-bridge 회로의 Switching 소자의 On/Off 특성에 의해 발생하는 전도성 노이즈 성분들을 Artificial Network(AN)에서 측정된 전자기 장해(EMI) 결과를 확인할 수 있었던 예제입니다.

그림 11. Motor Control System에서의 전도성 노이즈 시뮬레이션 결과

Electro Magnetic Susceptibility(EMS) 분석

전자기 민감성(EMS)은 앞서 소개 드렸던 것 같이 외부로부터 들어오는 노이즈가 전자기기에 얼마나 영향을 받는지에 대한 분석입니다. 전자기 민감성(EMS)의 측정의 경우 EUT(Equipment Under Test)를 동작시켜 놓은 상황에서 외부에서 인위적으로 만들어준 노이즈 신호에 의해 오작동이 나타날 경우 Fail, 오작동 없이 그대로 동작할 경우 Pass로 시험 평가를 진행합니다. 이때 외부에서 만들어준 노이즈가 어떠한 성분인지에 따라 아래의 분류로 나누어볼 수 있습니다. 그림 12에서 볼 수 있듯이 외부에서의 방사성 노이즈가 EUT에 영향을 주는 경우에 대한 분석은 Radiated Susceptibility(RS), 케이블과 같이 도체를 타고 들어오는 전도성 노이즈가 EUT에 주는 영향에 대한 분석을 Conducted Susceptibility(CS), 정전기 현상에 의해 발생하는 강한 전류가 EUT에 주는 영향에 대한 분석을 Electro static Discharge(ESD)라 합니다. 이 밖에도 다양한 종류의 전자기 민감성에 대한 시험들이 있으며, 이러한 시험에서 Fail이 될 경우 엔지니어는 민감성 시험을 Pass하기 위한 EMC 대책을 강구하여야 합니다.

그림 12. 노이즈 성분에 따른 전자기 민감성(EMS) 실험

하지만 실제 전자기 민감성(EMS) 시험은 외부의 노이즈를 인가하고 Pass/Fail에 대해서 확인하기 때문에, 외부 노이즈들이 어느 부분에 주로 영향을 주고, 어떠한 경로를 통해 영향을 주는지에 대한 부분은 시험을 통해 확인하기는 어려움이 있습니다. 이러한 경우 전자기장 해석을 이용하여 실험 환경을 모사한 상태에서 분석을 진행하면 시각적인 결과들을 통해 노이즈 보다 직관적으로 확인할 수 있습니다. 그림 13은 PCB에 정전기 내성 시험을 시뮬레이션 통해 진행해 봤던 사례로, ESD Gun을 통해 인가된 정전기 노이즈 신호가 어느 경로를 통해 전달되는지 시간의 흐름에 따라 확인 가능합니다. 또한 어느 부분에 전류가 강하게 몰려서 주요한 영향을 주게 되는지에 대한 부분도 분석해 볼 수 있습니다.

그림 13. 정전기 분석(ESD) 시 시간에 따른 전류 분포도 결과

이러한 전자기적 영향을 시각적으로 확인하게 되면 EMC 대책 수립을 더 수월하게 해보실 수 있습니다.

EMC 대책을 수립할 때 엔지니어는 다양한 방법들을 이용해 볼 수 있습니다. 그 중에서도 대표적인 방법은 대책 소자를 이용하는 방법입니다. 따라서 3D 구조와 다양한 소자들을 함께 두고 해석을 진행할 수 있어야 EMC 대책에 의한 변화를 결과로 확인할 수 있습니다. CST에서는 Circuit해석에 사용되는 CST DESIGN STUDIO를 제공하고 있으며, 해당 모듈을 사용할 경우 3D 구조에 다이오드, 트랜지스터와 같은 능동 소자들, EMC Filter 등을 함께 두고 해석을 진행할 수 있어 다양한 분석들을 진행해 보실 수 있습니다. 그림 14의 경우 3D PCB 모델에 강한 전류의 정전기 신호가 PCB로 인가했을 때의 해석인 ESD 분석을 진행했던 사례입니다. PCB 모델에 정전기 노이즈 신호가 인가될 시 PCB가 갖고 있는 다양한 Net들에서 전압을 측정했을 때 높은 값이 추출되는 결과를 확인하였습니다. 이를 방지하기 위해 Transient Voltage Suppression(TVS) 다이오드를 CST DESIGN STUDIO상에 Spice 파일로 불러와 Circuit을 구성하여 3D PCB 모델과 함께 해석을 진행하였습니다. TVS 다이오드는 과도 전압에 의한 디바이스의 고장을 막기 위해 자주 사용되는 능동 소자이기 때문에 각 Net에 높게 나타났던 전압을 낮추는 결과가 도출되는 것을 볼 수 있었습니다.

그림 14. Transient Voltage Suppression(TVS) 다이오드 유무에 따른 정전기 영향 분석

맺음말

다쏘시스템의 전자기 해석 솔루션인 CST STUDIO SUITE은 현재 전자기 적합성(EMC) 해석을 3D로 분석할 수 있는 소프트웨어입니다. 이는 PCB만 두고 해석을 진행하는 것이 아니라 PCB, 기구체, Enclosure 구조, EMC Test 환경 등이 있는 상황에서도 강력한 Meshing 기법을 이용한 Full 3D EM Simulation이 가능하여 보다 실질적인 결과물을 얻어낼 수 있습니다. 또한 전자기 적합성(EMC)의 각 세부 시험들(RE, CE, RS, CE, ESD 등)에 대한 해석을 CST STUDIO SUITE에서 제공하는 다양한 Product들과 Solver들을 이용하여 보다 효과적인 해석을 진행할 수 있습니다. 이러한 뚜렷한 강점들을 가지고 있는 CST STUDIO SUITE을 이용한 전자기 적합성(EMC) 해석을 통해 시각화된 전자기 노이즈 결과를 통해 전기, 전자기기에서의 영향 및 경로를 파악하여 보다 효과적인 전자기 분석 및 EMC 대책 수립을 경험해 보시길 바랍니다.

본 자료는 다쏘시스템 코리아 블로그의 자료로 자세한 내용은 아래 원본 링크를 통해 확인해 보시길 바랍니다.

원본 : 다쏘시스템코리아 블로그

관리자

2021.10.22

조회 1647

|